# 統計的遅延品質モデルを用いた 2サイクルゲート網羅故障テスト集合の評価

日大生産工（学部） ○片岡 瞭夫 日大生産工 細川 利典

京産大 吉村 正義 日大生産工 新井 雅之

## 1. まえがき

近年、半導体集積技術の発展に伴い、設計される超大規模集積回路(Very Large Scale Integrated circuits: VLSI)の大規模化、複雑化、高速化が急速に進展している。それに伴い不良VLSIにはセルや信号線に物理的欠陥が存在し、論理回路においても論理機能が故障により別な論理機能に変化する論理故障や本来の実動作速度でテストした場合に誤った動作をするタイミング故障など様々な故障が存在する[1]。

本論文では、回路のタイミングに関する欠陥を問題視し、信号線において発生する微小な遅延故障に着目する。遅延故障は、ゲートのスイッチング時間や配線の信号伝搬時間が増大し、本来起きるはずのフリップフロップ(Flip Flop: FF)の値の変化が規定の時間内に起こらない故障である。信号線における欠陥に対する遅延故障にはパス遅延故障や遷移遅延故障(Transition delay fault:TDF)などの故障モデルが存在する[2]。の中でもTDFモデルは、セルの入出力配線の欠陥により信号伝搬遅延が生じる故障をモデル化したものである。論理回路で遷移故障を表現する場合、ある一つの論理ゲートの入力または出力の信号線の伝搬遅延が増大する遅延故障として定義される。

本論文では、セル内の欠陥によって発生する遅延故障にも着目する。セル内の欠陥はレイアウト解析をおこなうことで、欠陥が存在するセルに対してどの入力系列でセルの出力信号線において故障励起可能か否かを判断する。セル内の欠陥によりセルの出力信号線の値が遷移する際に遅延が発生するような、セル内遅延欠陥をモデル化したものを2サイクルゲート網羅故障モデルと呼ぶ[3]。2サイクルゲート網羅故障モデルは各ゲートにおける出力信号線の値が遷移する場合、ゲートの各入力系列の印加で出力信号線の値が遅延する故障を仮定し定義する。

しかしながら、これらの故障モデルは検出する遅延欠陥のサイズを考慮しないため、微小な遅延欠陥を検出する能力が明らかではない。それゆえ、微小な遅延欠陥の検出能力を示す統計的遅延品質モデル(statistical delay quality model: SDQM)が提案された[4]。

SDQMは、まず各故障に対して遅延欠陥のサイズごとの発生確率、すなわち遅延欠陥分布を

仮定する。そして、与えられたテスト集合の遅延欠陥の検出能力を、テストタイミングとテストされた論理バスの遅延値の差で判定する。その際、テスト後に未検出となる遅延欠陥の発生確率を遅延欠陥分布より求める。

本論文では、SDQMに基づく遅延品質評価法を用いて遅延故障モデルのテスト集合を評価する。提案手法では、活性化遷移判定法[4]を用いて、遅延欠陥のサイズ(遅延値)を求め、その後、遅延欠陥分布をもとに統計的遅延品質レベル(statistical delay quality level: SDQL)を得る。本論文は、2サイクルゲート網羅故障モデルに対して、SDQMを用いて遅延品質を評価することを目的とする。

本論文の構成は以下のとおりである。第2章では、遷移故障モデル、2サイクルゲート網羅故障モデルについて説明し、第3章では、SDQMについて説明する。第4章では、SDQLの計算手法を説明し、第5章では、実験結果について説明する。最後に第6章でまとめと今後の課題を述べる。

## 2. 故障モデル

本章では、セル内の欠陥をモデル化した遷移故障モデルと2サイクルゲート網羅故障モデルについて説明する。2.1節で遷移故障モデルについて説明し、2.2節で2サイクルゲート網羅故障モデルについて説明する。

### 2.1 遷移故障モデル

遷移故障モデルは、セルの入出力配線の欠陥により信号伝搬遅延が生じる故障をモデル化したものである。論理回路で遷移故障を表現する場合、ある一つの論理ゲートの入力または出力の信号線の伝搬遅延が増大する遅延故障として定義される。遷移故障モデルには立上り遷移故障(slow-to-rise: STR)と、立下り遷移故障(slow-to-fall: STF)の2種類に分類できる。立上り遷移故障は、ある信号線において0から1への遷移が遅延する故障である。立下り遷移故障は、ある信号線において1から0への遷移が遅延する故障である。遷移故障モデルの遅延は、経路の長短にかかわらずFFでの影響が観測される。そのため、遅延のサイズは考慮していない。

---

An Evaluation of 2-Cycle Gate-Exhaustive Fault Test Sets

Using a Statistical Delay Quality Model

Akio KATAOKA, Toshinori HOSOKAWA, Masayoshi YOSHIMURA and Masayuki ARAI

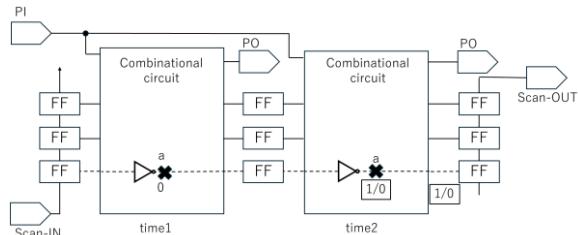

図 1 に遷移故障モデルの例を示す。図 1 において信号線  $a$  の 1 時刻目の論理値は 0, 2 時刻目は 0/1 である。論理値 0/1 は、正常値 0, 故障値 1 を示す。この時、信号線  $a$  において、論理値の 0 から 1 への遷移が遅延し立上り遷移故障が発生している。この故障は、故障の影響が FF まで伝搬されることで故障が検出される。

## 2.2 2 サイクルゲート網羅故障モデル

2 サイクルゲート網羅故障モデル[3]は、セル内の欠陥によりセルの出力信号線の値が遷移する際に遅延が発生する故障をモデル化したものである。各ゲートの各入力系列印加で出力信号線の値の遷移が遅延する故障を定義している。

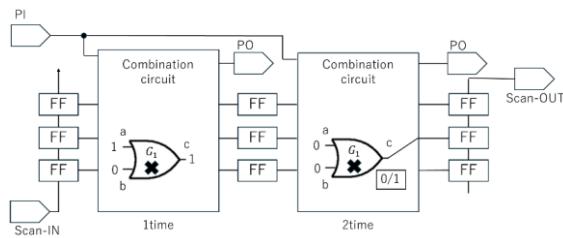

図 2 に 2 サイクルゲート網羅故障の例を示す。図 2 において、ゲート  $G_1$  における(1 時刻目の入力  $ab$ , 2 時刻目の入力  $ab$ )=(10,00)の時、出力信号線  $c$  の値が 1 から 0 に遷移する時間が遅延した故障を考えている。正常動作の場合、 $c$ =(1 時刻目, 2 時刻目)=(1,0)であるが、ゲート  $G_1$  内に故障が存在しているため、 $c$  は 1 から 0 への遷移で遅延が発生し、その遅延により FF に伝搬される値が次のクロックのキャプチャタイミングに間に合わず、正常値とは異なる値が取り込まれる。表 1 に 2 入力 OR の 2 サイクルゲート網羅故障集合を示す。出力信号線の値が遷移する場合の各入力系列の印加において故障を定義するため、ある OR ゲートの入力数を  $n$  とした場合、そのゲートにおける 2 サイクルゲート網羅故障数は  $2 \times (2^n - 1)$  個となる。表 1 の 2 サイクルゲート網羅故障数は  $2 \times (2^2 - 1) = 6$  である。 $f_1$  から  $f_3$  は、セル内欠陥により、出力信号線が 0 から 1 に立上り遷移する時間が遅延した故障であり、 $f_4$  から  $f_6$  は出力信号線が 1 から 0 に立下り遷移する時間が遅延した故障である。図 2 の故障例は表 1 の  $f_5$  に該当する。また、各ゲートの 2 サイクルゲート網羅故障集合は同一のテスト系列では検出されない独立故障集合である[5]。

図 1. 遷移故障モデルの例

図 2. 2 サイクルゲート網羅故障モデルの例

## 3. SDQM

本章では、SDQMについて説明する。3.1 節で遅延欠陥分布について説明し、3.2 節で SDQL について説明する。

### 3.1 遅延欠陥分布

遅延欠陥分布( $F(s)$ )は、遅延欠陥のサイズごとの発生確率を示す。ここで  $s$  は遅延値、 $F(s)$  はその発生確率を示す。遅延欠陥分布は実データの分析データの蓄積や、特別に設計されたテストチップ等により得られることが知られている[6]～[8]。

本論文では文献[4]で用いられている下記の式(1)を遅延欠陥分布とする。

$$F(s) = 1.58 \times 10^{-3} \times \exp(-2.1s) + 4.94 \times 10^{-6} \cdots (1)$$

### 3.2 SDQL

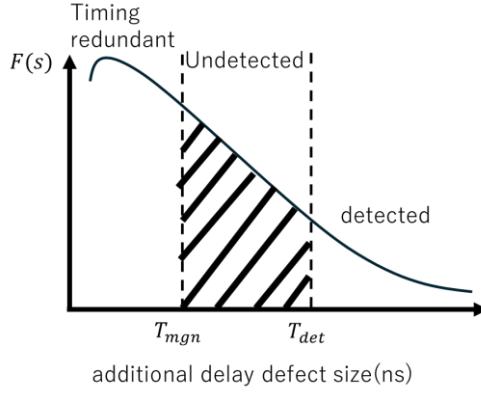

SDQL は、遅延欠陥の未検出となる割合を示す指標である。図 3 に遅延欠陥分布を示す。 $T_{mgn}$  は、システムクロックの周期から故障箇所を通る最長の論理バスの伝搬時間を差し引いた値を示す。すなわち、 $T_{mgn}$  は、システム動作に影響を及ぼす最小の遅延欠陥サイズである。 $T_{det}$  は、テストタイミングの周期から故障を活性化する最長バスの伝搬時間を差し引いた値を示す。すなわち、 $T_{det}$  は、与えられたテストパターンで実際に除去できる最小の遅延欠陥サイズである。したがって、欠陥による遅延値が  $T_{mgn}$  より小さい場合、タイミング冗長(Timing redundant)となり、 $T_{det}$  以上の場合、検出(detected)となる。このことから未検出(Undetected)となる領域は欠陥による遅延値が  $T_{mgn}$  から  $T_{det}$  の範囲である。すなわち、SDQL を求める式(2)は下記のとおりである。ここで、 $N$  は故障信号線数である。各信号線に対して、立上り遷移故障と立下り遷移故障が存在するため全故障数は  $2N$  となる。

$$\sum_{k=1}^{2N} \int_{T_{mgn}}^{T_{det}} F(s) ds \cdots (2)$$

表 1. 2 入力 OR ゲートにおける

2 サイクルゲート網羅故障集合

| Fault ID | input  |        | output |        |

|----------|--------|--------|--------|--------|

|          | 1-time | 2-time | 1-time | 2-time |

| $f_1$    | 00     | 01     |        |        |

| $f_2$    | 00     | 10     | 0      | 1/0    |

| $f_3$    | 00     | 11     |        |        |

| $f_4$    | 01     | 00     |        |        |

| $f_5$    | 10     | 00     | 1      | 0/1    |

| $f_6$    | 11     | 00     |        |        |

図 3. 遅延欠陥分布

#### 4. SDQL 計算手法

本章では、SDQL の計算手法について説明する。本論文では、活性化遷移判定手法[4]を用いる。図 4 に SDQL を計算する全体アルゴリズムを示す。入力は回路  $C$ 、テスト集合  $T$ 、故障集合  $FS$ 、遅延値  $DLV$  である。出力は SDQL である。

はじめに、各故障  $X (X \in FS)$  における故障箇所を通る最長の論理パスを求め、その信号伝搬時間をクロック周期から引く(1 行目)。その値を  $T_{mgn}(X)$  とする。テスト集合から 1 つテストパターン  $tp$ を取り出す(3 行目)。次に、論理シミュレーションをおこなう(4 行目)。その後、擬似外部入力(Pseudo Primary Input:PPI)から各ゲートの入出力ピンまでの信号伝搬時間( $D_{in}$ )を求める(5 行目)。ただし、複数の伝搬がある場合は、小さい方の信号伝搬時間を採用する。次に、2 サイクルゲート網羅故障シミュレーションをおこなう(6 行目)。続いて、故障箇所から擬似外部入力までの信号伝搬時間( $D_{in}(X)$ )を 5 行目で求めた信号伝搬時間とする(7 行目)。そして、故障箇所から擬似外部出力(Pseudo Primary Output:PPO)までの遅延値( $D_{out}(X)$ )が最大となる論理パスを求める(8 行目)。3 行目～8 行目までの工程をテストパターン数だけ繰り返す。次に、7 行目で求めた信号伝搬時間と 8 行目で求めた遅延値の和をテストパターンごとの各故障の信号伝搬時間とし、その中で最大となる信号伝搬時間をその故障の信号伝搬時間とする(10 行目)。そして、テスト周期( $T_{tim}$ )から 10 行目で求めた信号伝搬時間を差し引き、その値を  $T_{det}(X)$  とする(11 行目)。このとき、 $T_{det}(X)$  が  $T_{mgn}(X)$  と等しい場合は故障集合からその故障を削除する。その後、各故障の 1 行目で求めた  $T_{mgn}$  と 11 行目で求めた  $T_{det}$ 、遅延欠陥分布を用いて SDQL を計算する(12 行目)。最後に、求めた SDQL を返し終了する(13 行目)。

---

|                                                                         |

|-------------------------------------------------------------------------|

| Algorithm SDQL calculation                                              |

| Input : Circuit $C$ , Test Set $T$ , Fault Set $FS$ , Delay Value $DLV$ |

| Output : SDQL                                                           |

---

```

1.  $T_{mgn}(X) = \text{Delay\_Calc}(C, FS, DLV)$

2. While( $0 < |T|$ )then

3.   :  $T = T - \{tp\}$

4.   : Logic_Simulation( $C, tp$ )

5.   :  $D_{in} = \text{Delay\_Calc\_In}(C, tp, FS, DLV)$

6.   : Fault_Simulation( $C, FS$ )

7.   :  $D_{in}(X) = D_{in}$

8.   :  $D_{out}(X) = \text{Delay\_Calc\_Out}(C, tp, FS, DLV)$

9. endwhile

10.  $D(X) = D_{in}(X) + D_{out}(X)$

11.  $T_{det}(X) = T_{tim} - D(X)$

12. sdql = SDQL_Calc( $T_{mgn}(X), T_{det}(X), FS$ )

13. return(sdql)

14. end

```

---

図 4. 全体アルゴリズム

#### 5. 実験結果

本章では、実験結果について説明する。提案手法は C 言語で実装され、Core(TM) i7-1195G7 @ 2.90GHz、16GB メモリ搭載の PC を用いて実験をおこなった対象回路は ISCAS'89 ベンチマーク回路である。

遅延ファイルは `hosoken_syn_nonEX` の `sdf-1.0` を使用した。配線遅延は全て 1ns に設定した。また、遷移故障モデル、2 サイクルゲート網羅故障モデルの 2 つで故障シミュレーションをおこなった。テスト集合はどちらも故障検出効率が 100%となるものを使用した。そして、システムクロック周期とテストクロック周期を同じ値に設定した。

表 2 に実験結果を示す。表 2 において左から回路名、故障モデル、テストパターン数、故障数、SDQL である。また、表 2 の Trapezoid rule は台形則、Simpson's rule はシンプソン則を積分計算に用いた実験結果を示す。本実験では、クロック周期を 100ns、125ns、200ns に設定した。また、全ての論理パスの伝搬時間がクロック周期以内となる場合にのみ SDQL を求めている。

表 2 から、全ての回路において、TDF モデルより 2 サイクルゲート網羅故障モデルの SDQL が大きいことがわかる。長い経路を活性化しようとすると、活性化のために値が割当てられる信号線数が多くなる。したがって、それらを正当化するときに、故障の励起のために割当てた 1 時刻目と 2 時刻目の目標故障のゲートの入力値を正当化する範囲が重なり衝突を起こしていると考えられる。そのため、短い経路しか活性化できていないと考えられる。また、各回路での SDQL がどのクロック周期においても同じ値になっている理由としては、遅延欠陥分布の特性によるものと考えられる。

表 2. 実験結果

| Circuit | Fault model | Test pattern | Faults | SDQL           |                |                |                |                |                |

|---------|-------------|--------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|

|         |             |              |        | 100ns(10MHz)   |                | 125ns(8MHz)    |                | 200ns(5MHz)    |                |

|         |             |              |        | Trapezoid rule | Simpson's rule | Trapezoid rule | Simpson's rule | Trapezoid rule | Simpson's rule |

| s5378   | TDF         | 214          | 4315   | 0.169153       | 0.167478       | 0.169153       | 0.167478       | 0.169153       | 0.167478       |

|         | 2cycle      | 672          | 6556   | 1.001903       | 0.991983       | 1.001903       | 0.991983       | 1.001903       | 0.991983       |

| s9234   | TDF         | 352          | 8648   | -              | -              | 1.127335       | 1.115614       | 1.126351       | 1.115199       |

|         | 2cycle      | 1363         | 13533  | -              | -              | 4.138898       | 4.095432       | 4.135317       | 4.094373       |

| s13207  | TDF         | 432          | 11768  | -              | -              | -              | -              | 1.053526       | 1.043095       |

|         | 2cycle      | 1165         | 17119  | -              | -              | -              | -              | 3.94074        | 3.901723       |

| s15850  | TDF         | 285          | 12386  | -              | -              | -              | -              | 1.950861       | 1.931546       |

|         | 2cycle      | 304          | 16749  | -              | -              | -              | -              | 5.650907       | 5.594957       |

| s35932  | TDF         | 241          | 44076  | 2.624306       | 2.598323       | 2.624306       | 2.598323       | 2.624306       | 2.598323       |

|         | 2cycle      | 191          | 35901  | 7.589327       | 7.514185       | 7.589327       | 7.514185       | 7.589327       | 7.514185       |

| s38417  | TDF         | 333          | 48074  | -              | -              | 3.996665       | 3.957094       | 3.996664       | 3.957094       |

|         | 2cycle      | 1643         | 71748  | -              | -              | 16.998313      | 16.830012      | 16.998311      | 16.830011      |

| s38584  | TDF         | 986          | 43834  | -              | -              | -              | -              | 2.712889       | 2.686029       |

|         | 2cycle      | 1186         | 43456  | -              | -              | -              | -              | 7.498957       | 7.42471        |

## 6. むすび

本論文では、SDQMに基づく遅延品質評価法を用いて2つの遅延故障モデルのテスト集合を評価した。

実験結果から、TDFモデルに比べ、2サイクルゲート網羅故障モデルのSDQLが大きいことがわかった。ここから考えられる点として、短い経路しか活性化できていないことが挙げられる。

また、問題点として $T_{mgn}$ の計算で使用する論理パスを構造的に最長な論理パスにしていることが挙げられる。

今後の課題は、 $T_{mgn}$ の計算で使用する論理パスを活性化可能な最長の論理パスにし、より正確なSDQLの計算結果を得ることが挙げられる。

また2サイクルゲート網羅故障のテスト集合が活性化している故障伝搬経路の信号伝搬時間を評価することが挙げられる。

## 参考文献

- [1] 藤原秀, ディジタルシステムの設計とテスト, 工学図書株式会社, 2004

- [2] A.Kristic and K.T. Cheng, Delay Fault Testing for VLSI Circuits, Kluwer Academic Publishers, 1998.

- [3] Irith Pomeranz, "Efficient Identification of Undetectable Two-Cycle Gate-Exhaustive Faults", Proc.of IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, Volume:41 Issue 3.

- [4] 佐藤康夫, 浜田周治, 前田敏行, 高取厚夫, 野津山泰行, 梶原誠司, "統計的遅延品質モデル(SDQM)のフィージビリティ評価," 電子情報通信学会論文誌, vol.J89-D, no.8, pp.1717-1728, August 2006

- [5] S.B. Akers, C. Joseph, and B. Krishnamurthy, "On the Role of Independent Fault Sets in the Generation of Minimal Test Sets", in Proc. Intl. Test Conf, 1987, pp.1100-1107.

- [6] P. Nigh and A. Gattiker, "Test method evaluation experiments and data," Proc. IEEE International Test Conference, pp.454-463, 2000.

- [7] D.M. Wu and C.E. Radke, "Delay test effectiveness evaluation of LSSD-based VLSI logic circuits," Proc. ACM/IEEE Design Automation Conference, pp.291-295, 1991.

- [8] N.N. Tendolkar, "Analysis of timing failures due to random AC defects in VLSI modules," Proc. ACM/IEEE Design Automation Conference, pp.709-714, 1985.