スパッタ法で作製した MoS<sub>2</sub>薄膜の pn 制御と CMOS 評価

日大生産工(院) °土田 正道 日大生産工 清水 耕作

## 要約

これまでの研究で、スパッタ法で堆積された二硫化モリブデン薄膜は混入した酸素によって伝達特性を n から p に変化させることを明らかにしてきた。また電荷の移動には仕事関数と金属界面での欠陥が強く作用しているため、ソース・ドレイン電極に用いた金属の仕事関数も二硫化モリブデン薄膜の伝達特性に影響を与えていていることが分かっている。今回、チタンを電極の二硫化モリブデン薄膜トランジスタを用いた CMOS を作製した。結果、薄膜トランジスタから n 型と p 型をそれぞれ確認できた。これらを同一基板上に作製し出力波形を確認した結果、インバータ波形が確認できたことを報告する。

## 1. はじめに

近年、希少である貴金属やレアメタルが近年さらに高価になっていること、従来の半導体の供給が間に合っていないこともありトランジスタ(TFT)のコストが高くなっている。TFT で構成されている CMOS で使われている主な半導体材料はシリコンだが、プロセスが複雑で作製に時間がかかるのが課題だ。そこで我々は、比較的安価である二硫化モリブデン(MoS<sub>2</sub>)に注目し、電子デバイスへの応用を主に研究している。通常、単結晶として扱われているが本研究では、大面積に成膜するためにスパッタリング法で薄膜を形成した。本研究の目的は、高性能かつ大量生産が容易な MoS<sub>2</sub> - CMOS の作製プロセスの解明である。これまでの研究では、CMOS を構成する TFT の伝達特性を評価してきた。MoS<sub>2</sub> 膜内に混入している酸素量が TFT の伝達特性に影響を与えていることが分かっている。この影響力もソース・ドレイン(SD)に用いる金属の仕事関数によって変化することも分かった。

これらを踏まえて今回、同一基板上に n 型 TFT と p 型 TFT を形成させ、CMOS を作製した。この n 型側 TFT と p 型側 TFT それぞれの伝達特性の評価を行い、出力波形の確認を行った。

## 2 先行研究

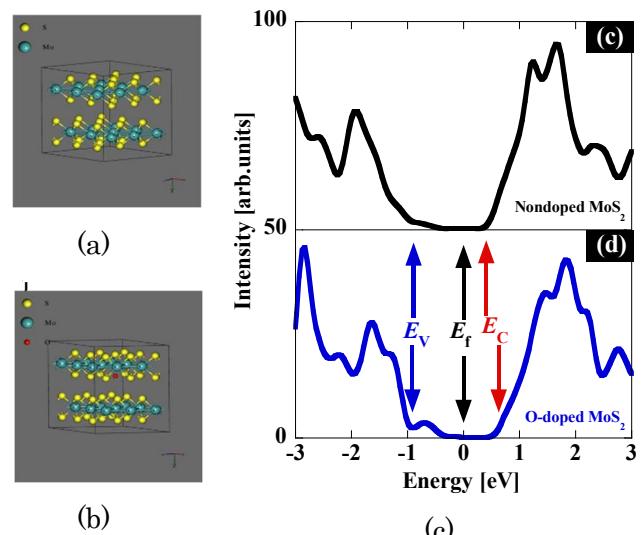

## 2-1 第一原理計算

MoS<sub>2</sub> のセル内に存在する硫黄原子を 1 個、酸素原子にランダムで置換したモデルを作成し、状態密度への影響を検討した。図 2(c)の横軸が 0 の位置をフェルミレベルとし、負の

領域は価電子帯側、正の値は伝導帯側のエネルギーを示している。

図 1. 第一原理計算の結果

図 1 より、酸素をドーピングしたとき、価電子帯端近傍に準位が形成されることがわかった。加えて、伝導帯端が高エネルギー側にシフトし、フェルミレベルが価電子帯寄りになっていることがわかる。これらより、酸素置換によって新たに形成された準位が電子アクセプタとなっていると考えられ、これが p 型になる原因であると考えできる。

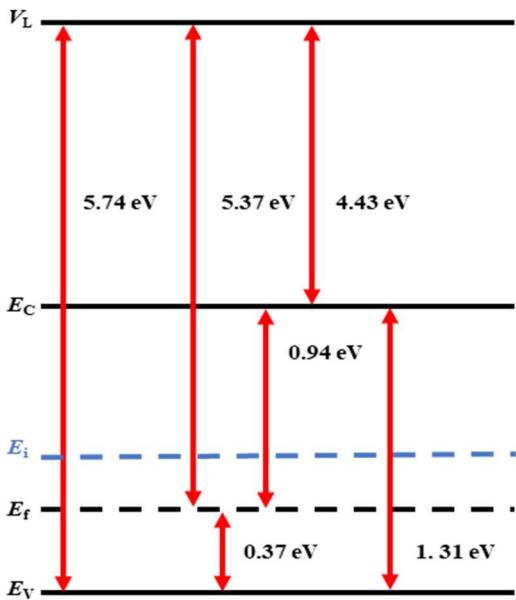

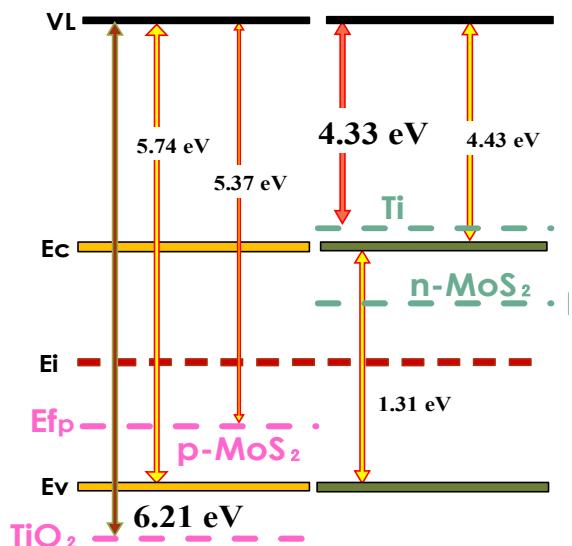

2-2 MoS<sub>2</sub> バンドプロファイル

PYS と IPES、KP を用いて作製された MoS<sub>2</sub> 薄膜のバンドプロファイルおよびフェルミレベルの位置を評価した。サンプルはグローブボックス中で調整し、真空中でアニールを行

った後、評価を行った結果、価電子帯端から0.37eVに存在することがわかる（図2）。さらにフェルミレベルが価電子帯により近い位置に存在することから、スパッタリング法で成膜した MoS<sub>2</sub>は p 型になることが確認できる。

図2. p-MoS<sub>2</sub>バンドプロファイル

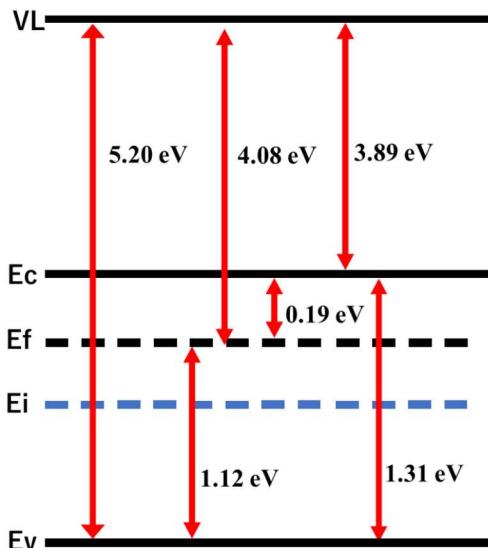

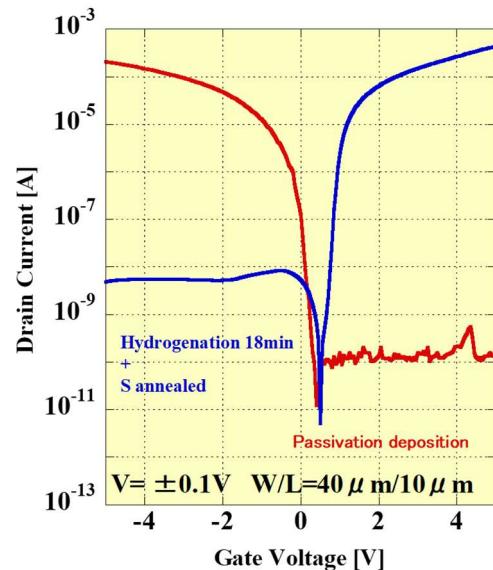

### 2-3 水素化によるn型化の伝達特性

図3のp型 TFT の伝達特性は、MoS<sub>2</sub>堆積後に酸素化と硫化アニールを行うことによって特性を改善したものでn型の伝達特性は、水素化したものである。P型 TFT の移動度とSS値は12.09[cm<sup>2</sup>/Vs], 193.3[mV/dec]であり、n型 TFT の移動度とSS値は15.95[cm<sup>2</sup>/Vs],

図3. n-MoS<sub>2</sub>のバンドプロファイル

137.8[mV/dec]でありほぼ同じ性能を得られた。n型になった原因是、原子状水素処理で膜の中に入れた原子状水素が膜中に取り込まれた酸素と結合して水となり、その後アニールをすることで水が蒸発し、膜から除去されたためであると考えている。

図4 原子状水素処理した MoS<sub>2</sub>の伝達特性

2-3 ソース・ドレイン電極に用いた金属の影響

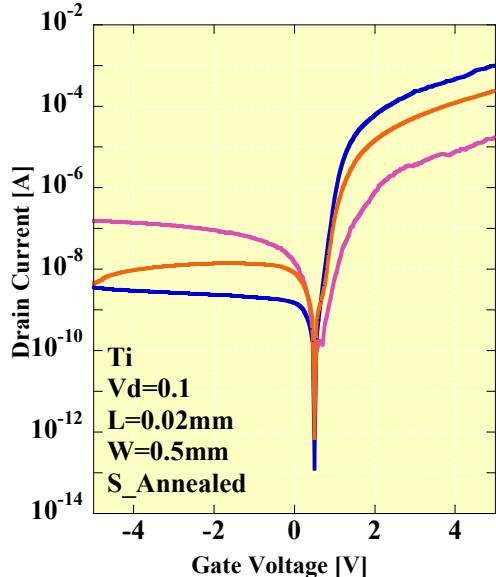

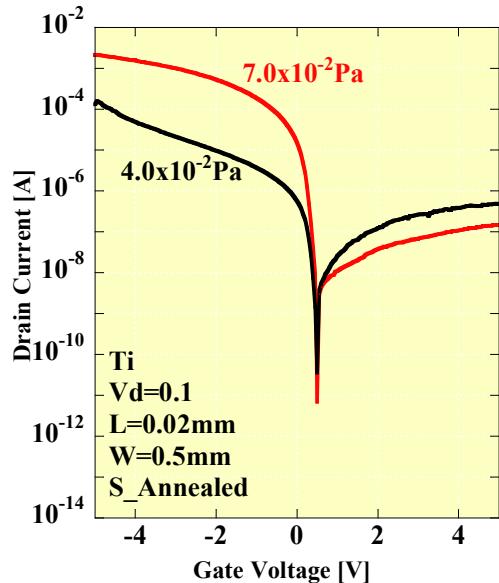

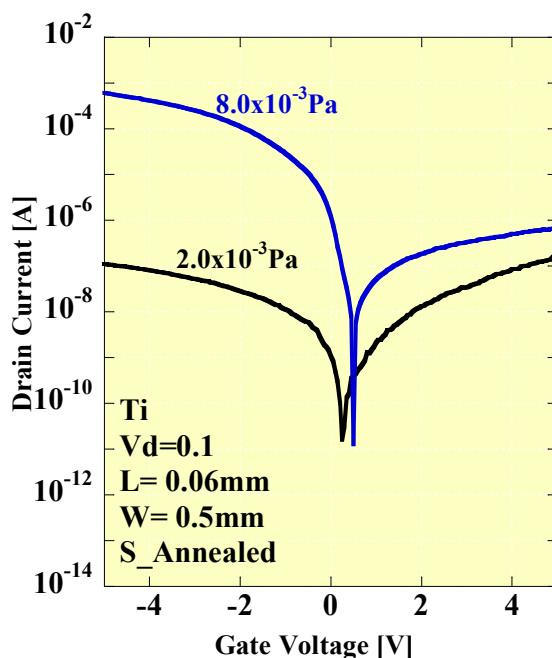

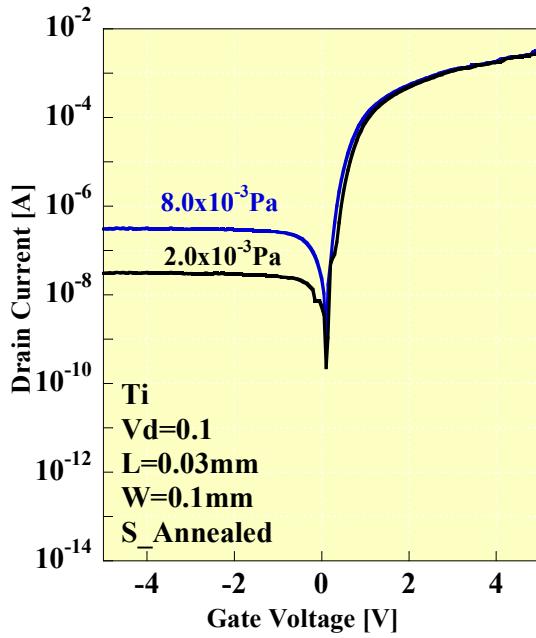

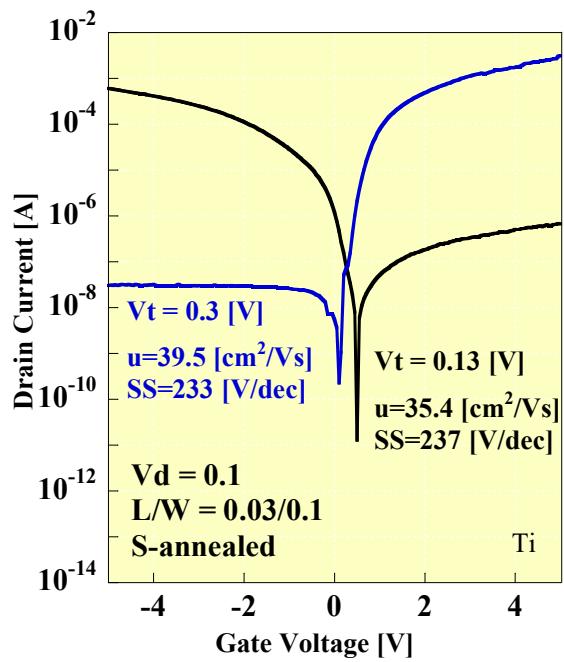

CMOSを作製するには、p型とn型のTFTをそれぞれ同一基板上に形成する必要がある。より少ないプロセスでCMOSを作製するために、SD電極をTiに固定し、原子状処理を行わずに背圧のみで酸素混入量を調整することでn型とp型を制御した（図6、図7）。

図5 電極のバンドプロファイル位置

同様の実験を Cu 電極で行ったが、こちらは n 型が確認できなかった。この結果から MoS<sub>2</sub> 薄膜は、ソース・ドレン電極に用いたい金属の仕事関数の影響を受けることが分かった。

### 3. 結果および考察

#### 3-1 CMOS を構成する n 型側 TFT と p 型側 TFT の伝達特性

Ti を SD 電極に用いることで p 型と n 型を両方作製できることが分かったので CMOS のパターンで基板を作製し、伝達特性を測定した。

ても硫黄との置換または、 $\text{MoS}_2$ への衝突が主な効果になるためと考えられる。つまり、酸素が混入してもほとんどが結合しないため、p型になりづらいと考えられる。

### 3-3 CMOS の出力波形

以上の結果を元に今回  $8.0 \times 10^{-3}$  Pa で  $\text{MoS}_2$  を成膜し n 型 TFT を作製。その後、p 型側 TFT のみ原子状酸素処理を施すことで p 型 TFT を作製した。この工程で、同一基板上にモノリシックに n 型と p 型の TFT を形成し、CMOS を作製した。各 TFT の伝達特性を測定した結果を図 10 に示す。p 型側からは p 型、n 型側からは n 型の伝達特性が得られた。

図 10 p-,n-TFT の伝達特性

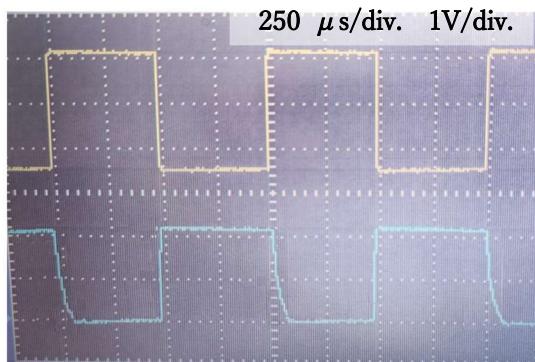

図 11  $\text{MoS}_2$  インバータ出力波形 (1kHz)

図 11 に示したのは作製した CMOS(インバータ)の入力波形と出力波形である。黄色線が入力波形で青線が出力波形を示している。インバータとして機能していることが確認できる

が、OFF へ切り替えるタイミングにゆがみが生じているため、遅くなっていることが分かる。このようになった原因として各 TFF の OFF 電流が高すぎることが挙げられる。OFF 電流が高い場合、消費電力が高くなり、回路全体が熱を持った結果、配線抵抗が上がりやすくなる。配線抵抗が上昇することで CR 時定数に影響を及ぼすため、スイッチング性能が悪化したと考えられる。

### 4. まとめ

CMOS のパターンで Si 基板上に作製し、n 型と p 型の両方の特性を得られた。これらを同一基板上に形成し CMOS を作製した結果、インバータとしての動作が確認できた。しかし 1kHz 以上の周波数で入力すると、方形波が崩れ始めることも確認できた。

今後はより高い周波数でも出力が出来るようにするために、原子状処理や硫化アニールの最適な条件を検討する。

### 参考文献

- [1] 李 柯澄, 清水 耕作, “スパッタ法で作製した p 型硫化モリブデン薄膜の特性と薄膜トランジスタへの応用” 日本材料学会, 2024 年 73 卷 9 号 p.735-742.