## 楽観推定フィールドランダムテスタビリティ向上のための

## 状態信号系列生成アルゴリズム

日大生産工（学部）○安島 悅平 日大生産工 細川 利典 京産大 吉村 正義

## 1. まえがき

近年、超大規模集積回路 (Very Large Scale Integrated circuits: VLSI) が社会の様々なシステムの中で利用されるようになり、医療機器、交通、自動車制御などの高い信頼性が要求されるものにも多く用いられている。一方で、半導体技術の発展により回路の複雑化、微細化、高速化が進み、製造ばらつきや回路の経年劣化が問題となっている[1,2]。特に、システム稼働中の回路の経年劣化に対しては、従来のライフタイム予測や出荷前の信頼性試験および寿命試験では限界があり、各 VLSI の実際の使用環境や動作条件の多様性によって、劣化進行の事前予測が困難である[2]。劣化による障害発生を防ぐ手段の一つとして、現状では動作マージン設計が行われているが、回路の製造ばらつき、動作環境、使用年数などの最悪の場合を考慮しながら決定するため、過大な動作マージンとなって VLSI の性能を犠牲にする可能性がある[1]。それゆえ、製造テストに加えて、過大な動作マージンを避けるために VLSI がシステムに搭載された後のフィールドテストが重要となる。

スキャン設計[3]と組込み自己テスト (Built-In Self-Test: BIST)[3]を組合せたスキャンベース BIST に基づくフィールドテスト手法[4-6]が提案されている。BIST は、他のテスト手法と比較して、実動作速度テストの適用が容易、テスト生成ツールの必要性の排除など、いくつかの利点[1,3]があるが、スキャンベース BIST に基づくフィールドテストではテスト実行時間の増大が課題として挙げられる。フィールドテストは電源オン/オフの短い時間で VLSI を網羅的にテストすることが理想である。テスト実行時間を削減する手法として、レジスタ転送レベル (Register Transfer Level: RTL) 回路に対する非スキャン BIST の故障検出率向上のための設計手法が提案されている[7-9]。しかしながら、文献[7]ではフィールドテストは考慮されていない。そのた

めフィールドテストに特化したアプローチとして、文献[10]では、RTL と論理回路の故障検出率との相関関係を示す評価尺度として推定フィールドランダムテスタビリティが提案された。文献[12]では、推定フィールドランダムテスタビリティ向上を図るために、データパスの各ハードウェア要素に対して、テスト実行回数が不足する数を算出し、不足しているテスト実行回数が多いハードウェア要素に対して、テスト可能な状態信号系列を生成した。しかしながら、文献[12]で生成した状態信号系列はすべてのハードウェア要素が完全テスト可能な実行回数を満たしていない。そのため文献[13]では、与えられた状態信号系列を用いてデータパスの動作を解析し、すべてのハードウェア要素に対して完全テスト可能な実行回数を満たす状態信号系列を生成する手法を提案された。しかしながら、文献[13]で生成した状態信号系列は、不足しているテスト実行回数が最も多いハードウェア要素から着目し、完全テスト可能な実行回数を満たす状態信号系列を生成する。これをすべてのハードウェア要素が完全テスト可能な実行回数を満たすまで繰り返すため、系列長が増大する。

本論文では、より短い状態信号系列で楽観構造的記号シミュレーションによる推定フィールドランダムテスタビリティをさらに改善することを目的とする。与えられたコントローラに対して、ある条件に基づいて状態信号系列をすべて列挙する。次にテスト実行回数が不足しているハードウェア要素に対して、全体の状態信号系列長が短くなるように、完全テスト可能な実行回数を満たす状態信号系列を生成する手法を提案する。

本論文は以下のように構成されている。第 2 章では、非スキャンベースのフィールドテストのテストのためのアキテクチャを述べる。第 3 章では、構造的記号シミュレーションを述べる。第 4 章では、推定フィールドランダムテスタビリティを述べる。第 5 章では、 $n$  回  $k$  連続状態遷移被覆を述べる。第 6 章では、楽観的に完全テスト可能な実行回数を満たす状態信号系列生成アルゴリズムを述べる。第 7 章では、高位設計ベンチマーク回路 kim[11]を用いた実験結果を示す。第 8 章では、結論と今後の課題を述べる。

## 2. 非スキャンベースフィールドテストアーキテクチャ

## 2.1. 非スキャンフィールドテスト

一般に、現状のフィールドテストではスキャンテストが用いられることが多い。これは、テストパターンとしてランダムパターンを用いた場合でも、ある程度高い故障検出率が保証されるためである。しかしながら、シフト動作時に各スキャンフリップフロップ (Flip-Flop: FF) に値を設定するため、シフト動作によるテスト実行時間の増大という問題点が挙げられる。この理由から、本論文では、非スキャンテストによるフィー

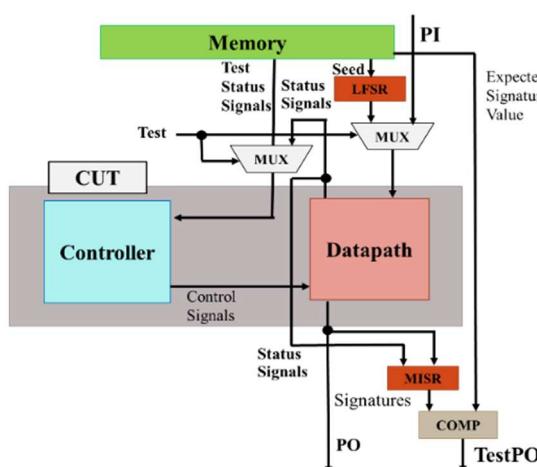

図 1. フィールドテストアーキテクチャ

ルドテストを対象とする。また、非スキャンテストの問題点である故障検出率を改善する手法を 2.2 節で説明する。

## 2.2. RTL フィールドテストアーキテクチャ

図 1 に RTL におけるフィールドテストアーキテクチャ[10]を示す。また、データパスとコントローラから構成される RTL 回路を研究対象とする。フィールドテスト手法を実現するために、LFSR の初期値となるシード値やシグネチャの期待値、状態遷移被覆によって生成した状態信号系列をメモリから与える。コントローラの入力は、データパスが output する状態信号とメモリに格納されているテスト用の状態信号をマルチプレクサを用いて選択可能とする。データパスの状態信号線は故障の影響を容易に観測するために、MISR に接続する。データパスの入力は、本来の外部入力の値と LFSR が output する擬似ランダムテストパターンをマルチプレクサにより選択可能とする。データパスの出力は、外部出力と MISR への入力に分岐する。MISR はデータパスの出力を圧縮し、シグネチャとして期待値とともに比較器に入力される。比較器は、シグネチャとその期待値との比較結果によって正常信号もしくは異常信号をテスト用外部出力 TestPO へ出力する。フィールドテスト用に挿入したマルチプレクサの制御信号線は新たに付加した外部入力 Test と接続する。

## 3. 構造的記号シミュレーション

データパスの構造と制御信号系列に基づいて行われるシミュレーションを構造的記号シミュレーションと呼ぶ[10]。構造的記号シミュレーションは、すべての時刻の外部入力、定数から可制御であることを示す C シンボル[10]を割当て、伝搬させる。また、外部出力と状態信号から入力方向に向けて可観測であることを示す O シンボル[10]を割当て、伝搬する。構造的記号シミュレーションはテスト実行可能な信号線を判定するために行われる。データパスはハードウェア要素とそれらを接続する信号線、及びコントローラへ出力する状態信号線から構成される。ハードウェア要素は多入力 1 出力の演算器、マルチプレクサ、レジスタ、外部入力、定数、外部出力、信号線、制御信号線がある。以下に、構造的記号シミュレーションで用いられる用語について定義する。

### (定義 1 : テスト可能な信号線)

時刻  $t$  で、ある信号線に C シンボルと O シンボルが割当てられている時、その信号線を時刻  $t$  でテスト可能な信号線という。

### (定義 2 : テスト実行回数)

データパスのある信号線がテスト可能である時刻数をその信号線のテスト実行回数という。

### (定義 3 : 完全テスト可能な実行回数)

完全テスト可能な実行回数とは、各ハードウェア要素を論理回路に変換し、擬似ランダムパターンを印加したときに故障検出率が 100%以上となるために必要な擬似ランダムパターン数である。

### (定義 4 : 楽観構造的記号シミュレーション)

楽観構造的記号シミュレーション[12]は構造的記号シミュレーション[10]の処理とほぼ同じであり、あるハードウェア要素がテスト可能となるようにドントケ

ア (X) に論理値が割当てられていることを仮定する。各状態遷移における X の論理値割当てにより、テスト可能なハードウェア要素を最大限に見積る。

## 4. 推定フィールドランダムテスタビリティ

本論文では、RTL でのテスタビリティの評価尺度として、推定フィールドランダムテスタビリティ[10]を用いる。以下に推定フィールドランダムテスタビリティで用いられる用語について定義する。

### (定義 5 : 楽観推定フィールドランダムテスタビリティ)

楽観構造的記号シミュレーションによって得られた推定フィールドランダムテスタビリティを楽観推定フィールドランダムテスタビリティという。

### (定義 6 : 完全楽観推定フィールドランダムテスタビリティ)

回路全体の楽観推定フィールドランダムテスタビリティが 100%を達成しているときの推定フィールドランダムテスタビリティを完全楽観推定フィールドランダムテスタビリティという。

## 5. $n$ 回 $k$ 連続状態遷移被覆

コントローラに入力する状態信号系列は決定論的パターンを用いる。これにより、コントローラに任意の状態遷移の動作を実行させることができるとなる。その際、故障検出率向上のために、与える状態信号系列が重要となる。文献[10]では、全ての  $k$  連続( $k$  は自然数)状態遷移を被覆するための状態信号系列を与える。一般に、テストパターンとして擬似ランダムパターンを用いる場合、回路動作に偏りが生じ、未検出故障数が増加する可能性がある。それゆえ、コントローラの全ての  $k$  連続状態遷移を少なくとも 1 回実行することで、可能な限り回路動作が偏らないようにし、新たな故障を検出する可能性を向上させる。また、更なる故障検出率の向上を達成するため、全ての状態遷移を少なくとも  $n$  回( $n$  は自然数)被覆するような状態信号系列生成を行う。

## 6. 状態信号系列生成アルゴリズム

はじめに、対象となる RTL 回路に  $n$  回  $k$  連続状態遷移被覆を用いた状態信号系列に対して、楽観構造的記号シミュレーションを実行し、各ハードウェア要素のテスト実行回数を算出する。次に完全テスト可能な実

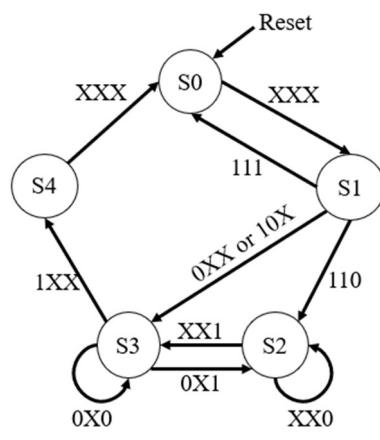

図 2. 例題コントローラ

行回数を満たしていないハードウェア要素に対して、ある条件に基づく状態信号系列をすべて列挙し、完全テスト可能な実行回数を満たすような状態信号系列を生成する。ある条件に基づく状態信号系列の列挙例を示す。図2に例題コントローラを示す。S0を初期状態とする。ここで、状態信号系列長の範囲は、2から初期状態から初期状態までの連続した状態遷移の最大系列長とする。図2では、S0→S1→S2→S3→S4→S0の6が初期状態から初期状態までの連続した状態遷移の最大系列長となる。次にある条件に基づくすべての状態信号系列に対して、楽観構造的記号シミュレーションを実行し、ハードウェア要素のテスト実行回数を算出する。表1は長さ2, 3, 4, 5, 6の各状態信号系列に対して、楽観構造的記号シミュレーションを実行したときのハードウェア要素のテスト実行回数例である。ある状態信号系列では、REG0, REG1, REG2, SUB0のテスト実行回数が完全テスト可能な実行回数を満たしていない。そのため、この4つのハードウェア要素に対して、テスト実行している系列を探索する。表1では長さ5のパターン1, パターン2がこの条件を満たしつつ、全体の状態信号系列長を短くすることができる。それゆえ、パラメータ5のパターン1, パターン2の状態信号系列を完全テスト可能な実行回数を満たせるまで繰返し追加する。パターン1を3回、パターン2を1回繰返し追加すると、各ハードウェア要素のテスト実行回数において、REG0は15回、REG1は15回、REG2は11回、SUB0は29回となり、完全テスト可能な実行回数を満たす。

## 7. 実験結果

本実験では、高位設計ベンチマーク回路kim[11]、を対象回路とする。コントローラに対して、1回1連続状態遷移被覆する状態信号系列を生成する。その後、楽観構造的記号シミュレーションを実行し、各ハードウェア要素のテスト実行回数を算出する。完全テスト可能な実行回数を満たしていないハードウェア要素に対して、追加する系列の長さと状態信号系列の挿入回数を決定する。その後、長さに基づく状態信号系列を挿入回数分、追加する。その結果、楽観構造的記号シミュレーションにより、すべてのハードウェア要素が完全テスト可能な実行回数を満たしているか算出する。

表2にkim[11]の各長さにおけるテスト実行回数の実験結果を示す。3行目に完全テスト可能な実行回数を示す。4行目から14行目に各長さにおける各パターンのテスト実行回数を示す。

表2の実験結果より、長さが増加すると、テスト実行回数が増加する傾向にある。例えば、長さ12のパターン3は、各ハードウェア要素のテスト実行回数は10回以下である。しかし、長さ15のパターン2は、ADD0を除いた各ハードウェア要素のテスト実行回数が増加している。これは、長さの増加は系列長の増加と同じであるため、長さが増加するとテスト実行回数が増加する。また、同じ長さの各パターンにおけるテスト実行回数は、パターンにおいて変化がある。例えば、長さ13のパターン1のREG4のテスト実行回数は0回、REG5のテスト実行回数は0回である。パターン2では、REG4のテスト実行回数は10回、REG5のテスト

表1. 各ハードウェア要素のテスト実行回数例

|                |         | ハードウェア要素 |      |      |      |

|----------------|---------|----------|------|------|------|

|                |         | REG0     | REG1 | REG2 | SUB0 |

| 完全テスト可能な実行回数   |         | 8        | 8    | 8    | 29   |

| 状態信号系列のテスト実行回数 |         | 6        | 6    | 3    | 18   |

| 長さ             | 2 パターン1 | 1        | 1    | 0    | 0    |

|                | パターン1   | 1        | 1    | 1    | 0    |

|                | 3 パターン2 | 2        | 2    | 0    | 0    |

|                | パターン3   | 1        | 1    | 1    | 1    |

|                | 4 パターン1 | 2        | 2    | 2    | 1    |

|                | パターン2   | 3        | 3    | 1    | 2    |

| 5              | パターン1   | 2        | 2    | 2    | 3    |

|                | パターン2   | 3        | 3    | 2    | 2    |

|                | パターン3   | 4        | 4    | 3    | 1    |

| 6              | パターン1   | 5        | 5    | 3    | 2    |

実行回数は5回である。これは、状態信号系列によって、レジスタやマルチプレクサの制御信号値が変化するため、ハードウェア要素がテスト可能にならない可能性があると考えられる。

表3にkim[11]の1回1連続状態遷移被覆における実験結果を示す。3行目に完全テスト可能な実行回数を示す。4行目に1回1連続状態遷移被覆におけるテスト実行回数、系列長、推定フィールドランダムテストビリティを示す。5行目に提案手法で生成した状態信号系列のテスト実行回数、系列長、推定フィールドランダムテストビリティを示す。提案手法は、表2における長さ12のパターン1を6回、パターン2を1回挿入する。

表3の実験結果より、1回1連続状態遷移被覆する状態信号系列に対して、SUB0, ADD0, ADD1の3個のハードウェア要素が完全テスト可能な実行回数を満たすことができた。また、推定フィールドランダムテストビリティは1回1連続状態遷移被覆は97.48%、提案手法は98.30%であり、0.82%増加している。系列長は1回1連続状態遷移被覆は37、提案手法は121であり、84増加している。各ハードウェア要素において、完全テスト可能な実行回数と実行回数の差分が大きいハードウェア要素が完全テスト可能な実行回数を満たすのに困難である。ADD1の完全テスト可能な実行回数は43回、1回1連続状態遷移被覆のテスト実行回数は11回であり、差分が32回と一番大きい。また、提案手法のテスト実行回数は44回であり、差分は1回と一番小さい。ゆえに、各ハードウェア要素が完全テスト可能な実行回数を満たすのが困難であるほど、状態信号系列の挿入回数が増加するため、系列長が増加すると考えられる。

## 8. むすび

本論文では、n回k連続状態遷移被覆する状態信号系列を用いて、楽観構造的記号シミュレーションの実行後の完全テスト可能な実行回数を満たしていない各ハードウェア要素に対して、完全テスト可能な実行回数を満たすための、状態信号系列を生成する手法を提案した。適切な系列の長さと状態信号系列の挿入回数を決定することで、各ハードウェア要素における完全

表2. *kim* の各長さにおけるテスト実行回数

|              |       | ハードウェア要素 |      |      |      |      |      |      |      |      |       |      |      |

|--------------|-------|----------|------|------|------|------|------|------|------|------|-------|------|------|

|              |       | REG0     | REG1 | REG2 | REG3 | REG4 | REG5 | REG6 | SUB0 | SUB1 | LESS0 | ADD0 | ADD1 |

| 完全テスト可能な実行回数 |       | 8        | 8    | 8    | 8    | 8    | 8    | 8    | 29   | -    | -     | 43   | 43   |

| 長さ           | 12    | パターン1    | 9    | 10   | 10   | 7    | 0    | 0    | 9    | 4    | 1     | 9    | 4    |

|              | 12    | パターン2    | 9    | 10   | 10   | 9    | 4    | 5    | 9    | 6    | 4     | 9    | 5    |

|              | 12    | パターン3    | 9    | 10   | 10   | 7    | 8    | 3    | 7    | 6    | 2     | 9    | 8    |

|              | 13    | パターン1    | 10   | 11   | 11   | 8    | 0    | 0    | 10   | 5    | 1     | 10   | 5    |

|              | 13    | パターン2    | 10   | 11   | 11   | 9    | 10   | 5    | 9    | 6    | 4     | 10   | 6    |

|              | 13    | パターン3    | 10   | 11   | 11   | 8    | 8    | 3    | 7    | 8    | 2     | 10   | 8    |

| 14           | パターン1 | 11       | 12   | 12   | 8    | 11   | 0    | 10   | 5    | 1    | 11    | 6    | 3    |

|              | 14    | パターン2    | 11   | 12   | 12   | 9    | 10   | 5    | 9    | 6    | 4     | 11   | 7    |

|              | 14    | パターン3    | 12   | 13   | 13   | 8    | 11   | 0    | 19   | 5    | 1     | 12   | 7    |

|              | 15    | パターン1    | 12   | 13   | 13   | 10   | 10   | 5    | 9    | 8    | 4     | 12   | 7    |

| 16           | パターン2 | 12       | 13   | 13   | 10   | 10   | 5    | 9    | 8    | 4    | 12    | 7    | 5    |

|              | 16    | パターン1    | 13   | 14   | 14   | 9    | 11   | 0    | 19   | 7    | 1     | 13   | 7    |

表3. *kim* の1回1連続状態遷移被覆における実験結果

|                          |  | ハードウェア要素 |      |      |      |      |      |      |      |      |       |      | 系列長  | EFRT(%) |       |

|--------------------------|--|----------|------|------|------|------|------|------|------|------|-------|------|------|---------|-------|

|                          |  | REG0     | REG1 | REG2 | REG3 | REG4 | REG5 | REG6 | SUB0 | SUB1 | LESS0 | ADD0 | ADD1 |         |       |

| 完全テスト可能な実行回数             |  | 8        | 8    | 8    | 8    | 8    | 8    | 8    | 29   | -    | -     | 43   | 43   |         |       |

| 1回1連続状態遷移被覆              |  | 34       | 35   | 35   | 24   | 29   | 30   | 30   | 20   | 8    | 34    | 20   | 11   | 37      | 97.48 |

| 提案手法<br>(長さ12:パターン1,2採用) |  | 104      | 112  | 112  | 88   | 89   | 60   | 96   | 62   | 34   | 104   | 61   | 44   | 121     | 98.30 |

テスト可能な実行回数を満たし、推定フィールドランダムテストビリティを向上することができた。

今後の課題としては、適切な系列の長さと状態信号系列の挿入回数の決定に対して、擬似ブール最適化問題(Pseudo Boolean Optimization : PBO)[14]で定式化することが挙げられる。

## 参考文献

- [1] 藤原秀雄, “デジタルシステムの設計とテスト,” 工学図書株式会社, 2004.

- [2] I.Moghaddasi, S.Gorgin and J.Lee, “Dependable DNN Accelerator for Safety-Critical Systems: A Review on the Aging Perspective,” IEEE Access, vol.11, pp. 89803-89834, 2023.

- [3] L.Wang, C.Wu and X.Wen, “VLSI Test Principles and Architectures: Design for Testability,” Morgan Kaufmann Publishers, 2006.

- [4] Tobias Strauch, “Non-interfering Online and In-field SoC Testing,” 2024 IEEE International Workshop on Rapid System Prototyping (RSP), pp.42-48, 2024.

- [5] Irith Pomeranz, “Chip Aging and Double Transition Faults,” 2025 IEEE International Test Conference (ITC), pp.1-7, 2025.

- [6] Irith Pomeranz, “Varying Periods of In-Field Testing With Storage and Counter Based Logic Built-In Self-Test,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2025.

- [7] A.Ahmadi, N.Paraman, M.S.Rusli and S.Issak, “Hybrid non scan with built-in self-test for fault coverage improvement,” AIP Conference Proceedings, vol. 2795, 2023.

- [8] K. Yamaguchi, H. Wada, T. Masuzawa, H. Fujiwara, “A BIST Method Based on Concurrent Single-Control Testability of RTL Data Paths,” Proceedings 10th Asian Test Symposium, pp.313-318, 2001.

- [9] K. Yamaguchi, M. Inoue, H. Fujiwara, “Hierarchical BIST: Test-Per-Clock BIST with Low Overhead,” Electronics and Communications in Japan, Vol.90, No.6, 2007.

- [10] Y. Toyooka, H. Watanabe, T. Hosokawa, M. Yoshimura, “An Evaluation of Estimated Field Random Testability for Data Paths at Register Transfer Level Using Status Signal Sequences Based on k-Consecutive State Transitions for Field Testing,” 2023 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pp.1-6, 2023.

- [11] M. T. -C. Lee, “High-Level Test Synthesis of Digital VLSI Circuits,” Artech House Publishers, 1997.

- [12] 豊岡雄大, 細川利典, 吉村正義, “レジスタ転送レジストにおけるデータバスの推定フィールドランダムテストビリティ改善のための追加状態信号系列生成について” 信学技報, vol.123, no.389, DC2023-102, pp.47-52, 2024年2月.

- [13] 廣瀬恭介, 細川利典, 吉村正義, “集約推定フィールドランダムテストビリティ向上のための状態信号系列生成手法” 信学技報, vol.124, no.374, DC2024-114, pp.47-52, 2025.

- [14] V. Manquinho, R. Martins and I. Lynce, “Improving Unsatisfiability-Based Algorithms for Boolean Optimization”, Theory and Applications of Satisfiability Testing-SAT 2010.