# 光電子制御プラズマ CVD による絶縁性 DLC 成膜の研究

○関 理志<sup>1</sup>、小川 修一<sup>2</sup>、岡田 光博<sup>3</sup>、沖川 侑輝<sup>3</sup>、山田 貴壽<sup>3</sup>

## 1. まえがき

グラフェンは極めて高いキャリア移動度を示すため、次世代の高性能トランジスタであるグラフェンチャネルを用いる電界効果トランジスタ (FET) のチャネル材料として期待されている。しかし、ゲート絶縁膜として用いられる  $\text{SiO}_2$  などの酸化物は、酸素がグラフェンに侵入し欠陥を与える可能性が指摘されているため、酸素を含まない絶縁膜の検討が重要である<sup>1)</sup>。その候補の一つであるダイヤモンドライカーボン (DLC) は、優れた絶縁性と機械的特性を併せ持ち、グラフェンFETのゲート絶縁膜として有望視されている。

DLCの成膜方法として、光電子放出をトリガーにプラズマを生成する光電子制御プラズマ CVD (PA-PECVD) が注目されている<sup>1)</sup>。PA-PECVDでは基板に波長172 nmの紫外光を照射し、基板から放出された光電子がプラズマ生成を開始する<sup>2)</sup>。この手法は大面積での均一プラズマ生成に適する一方、金属ステージなど基板以外の部分からの光電子放出があるとプラズマ分布が変化し、膜成長条件や膜特性に影響を与える可能性がある。これらの背景に基づき、本研究ではステージ全面にプラズマを生成して成膜した試料 (サンプル1) と穴あきガラスカバーを被せ、光電子放出領域を基板部のみに限定して成膜した試料 (サンプル2) の電気特性を比較した。

## 2. 提案手法

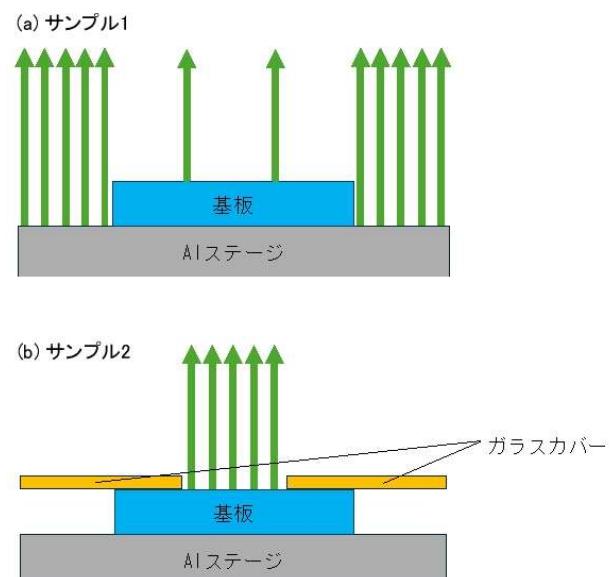

PA-PECVDの成膜方法として、サンプル1は、Si (001) 基板をそのままステージ上に載せ、紫外光照射によりステージ全面にプラズマを生成してDLCを成膜する手法を行った。サンプル2は、Si基板上に穴あきガラスカバーを被せ、紫外光が開口部からのみ基板にのみ到達するようにして、光電子放出領域をSi基板部に限定してDLCを成膜する手法。

これにより金属ステージなど基板以外からの光電子放出が抑制され、プラズマは開口部付近に局所化することが期待される。この操作により、金属ステージ由来の光電子放出が低減さ

れ、結果としてプラズマ中のイオンの照射分布やイオン衝突頻度が影響を与える。

## 3. 実験方法および測定方法

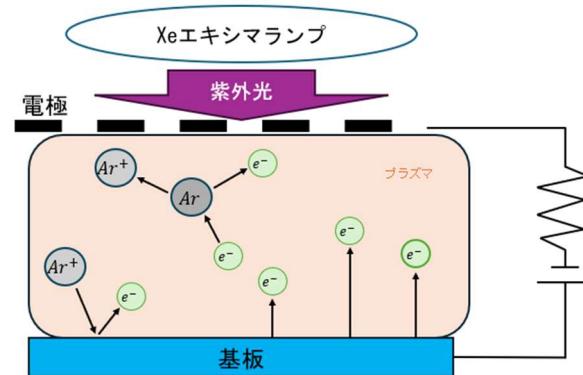

成膜はPA-PECVD装置を用い、Si (001) 基板上に穴あきガラスカバーを被せていない場合と穴あきガラスカバーを被せた場合の2種類DLC成膜をした。光電子制御プラズマCVDの概要図をFig.1に示す。

Fig.1 光電子制御プラズマの概要図

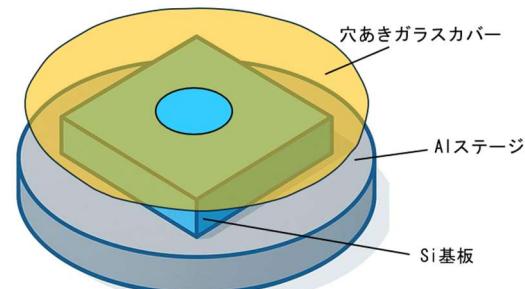

ガラスカバー無しではステージ全面にプラズマが広がるのに対し、Fig.2に示すようにガラスカバー付きでは開口付近に局所的なプラズマが形成された。成膜条件を表1に示す。

Fig.2 穴あきガラスカバーの概要図

成膜後のDLC膜の電気抵抗は四探針法で室温・大気中にて評価した。使用プローブは先端径160  $\mu\text{m}$ 、探針間隔1 mmの共和理研製を用い、

Study on insulating DLC film formation by photoelectron controlled plasma CVD

Satoshi SEKI, Shuichi OGAWA, Mitsuhiro OKADA, Yuki OKIGAWA and Takatoshi YAMADA

直流定電流源 (Advantest R6142) で電流を印加し、電圧はデジタルマルチメータ (ADCMT 7352E) で記録した。測定手順は標準的な四探針シート抵抗測定法に準拠した。測定不能な高抵抗サンプルに対しては装置感度と測定上限から抵抗の測定限界を評価した。

表 1. 成膜条件

|            | サンプル1 | サンプル2 |

|------------|-------|-------|

| ガラスカバーの有無  | なし    | あり    |

| CH4[sccm]  | 10    | 10    |

| Ar[sccm]   | 90    | 90    |

| 圧力[Pa]     | 200   | 200   |

| ステージ温度[°C] | 100   | 100   |

| 成膜時間[min]  | 30    | 30    |

#### 4. 実験結果および検討

サンプル1の四探針測定によるシート抵抗は約42.47  $\Omega/\text{sq}$  と得られた。サンプル2は四探針での有効測定が困難なくらい高抵抗であり、装置特性から見積もってシート抵抗  $\gtrsim 2.0 \times 10^5 \Omega/\text{sq}$  と評価された。サンプル1およびサンプル2は、プラズマ発生領域の違いが膜成長の動的環境に与える影響に起因すると考えられる。具体的には次のように整理できる。

金属ステージは仕事関数が低い場合、紫外光照射で光電子を放出しやすく、それにより広範囲にプラズマが生成される。結果としてプラズマ中のイオンはステージ方向へ偏りやすく、基板表面へのイオン衝突頻度やエネルギースペクトルがサンプル全面で均一にならない可能性がある。この条件下では、より導電性の高いDLC成膜が観察された。

Fig.3に示すように穴あきガラスカバーによりSi基板部以外からの光電子放出を抑制されると、プラズマは開口部の周辺に局所化する。これによりDLCに対するイオン衝突が頻繁に起こることで膜の硬さや密度が向上し<sup>3)</sup>、その結果として抵抗率も上昇したと考えられる。

#### 5. まとめ

本研究では、PA-PECVDを用いてSi (001) 基板上にDLC絶縁膜を成膜し、プラズマ発生領域を基板部に限定することが膜の電気特性に与える影響を評価した。主な結論は以下の通りである。ガラスカバー無しで成膜したDLC (サンプル1) は四探針で 約42.47  $\Omega/\text{sq}$  を示したのに対し、ガラスカバー有り (サンプル2) は非常

に高抵抗で  $\gtrsim 2.0 \times 10^5 \Omega/\text{sq}$  と評価された。本結果は、光電子放出領域を制御することにより、成膜時のイオン照射分布が変化し、膜中の構造的欠陥や密度に影響を及ぼす可能性を示唆している。これにより、DLC膜の絶縁性および信頼性を高める成膜プロセスの最適化が期待される。さらに、本手法はグラフェンFETなどの高性能電子デバイスへの応用においても有用であると考えられる。

以上より、基板からの光電子放出領域をガラスカバーによるプラズマの発生領域制御によりイオン衝突頻度や局所的電場が変化し、電気特性が変わったと考えられる。これにより、DLC膜の高抵抗化と膜質改善およびトランジスタ用絶縁膜への応用に期待できると示唆された。

Fig.3 ガラスカバーの有無においての断面図

#### 参考文献

- 1) Yang, M.; Ogawa, S.; Takabayashi, S.; Otsuji, T.; Takakuwa, Y. "Formation of Diamond-Like Carbon Films by Photoemission-Assisted Plasma-Enhanced Chemical Vapor Deposition." *Thin Solid Films*, 523 (2012) 25–28.

- 2) Ajia, S.; Ogawa, S.; Kamata, N.; Takakuwa, Y. "Flattening of copper surfaces with a low energy xenon-ion source generated by photoemission-assisted plasma." *Japanese Journal of Applied Physics*, 58 (2019) 090911 (1–5).

- 3) Tanaka, A. "Mechanical Properties of DLC Films. *Journal of Vacuum Society of Japan*, 47 (2004)