## 故障診断分解能向上のためのマルチプレクサのデフォルト入力を用いた制御ポイント挿入の一考察

日大生産工(院) ○YUN YEONGKYEONG 日大生産工 細川 利典

京都産業大 吉村 正義 明治大 山崎 浩二

### 1. はじめに

近年, 半導体微細化技術の進歩に伴い, 超大規模集積回路(Very Large Scale Integrated circuits : VLSI)において, 異常動作の物理的な原因を特定する故障解析[1]は, 歩留まり[2]向上のために重要である. 故障解析では, 電子顕微鏡などを用いて故障 VLSI 内部の観測を行うため, 多大なコストを要する. そのため, 故障 VLSI に存在する可能性のある故障(被疑故障)を事前に絞り込んでおく故障診断[3]が, 故障解析コスト低減のために重要である. 故障診断を行うことで故障 VLSI の異常な外部出力応答を裏付けることのできる故障箇所を推定する. このとき, テストに使用したテスト集合で識別可能な故障ペア数が多いほど, 被疑故障数を削減することができ, 故障診断における診断分解能が向上する.

診断分解能を向上させる診断容易化設計(Design for Diagnosability : DFD)手法[4]-[6]やゲートレベルにおける観測ポイント挿入(Observation Point Insertion : OPI)[7],[8]などの診断分解能向上を考慮した設計手法が提案されており, 被疑故障数を削減できることができることが報告されている. しかしながら, ゲートレベルで挿入された観測ポイントによる回路面積の増大やタイミングの最適性が損失するなどの課題が挙げられている. また, 製造用テスト集合では診断分解能が十分でないことからゲートレベルにおいて診断分解能を考慮したテスト生成手法[9]が提案されている. しかしながら, 回路構造によってはテスト生成において診断分解能を向上させることができ困難な場合がある. また, 文献[6]では抽象度の高いレジスタ転送レベル (Register Transfer Level : RTL) における構造的記号シミュレーション[5]で得られた情報を用いて識別可能な故障ペア推定数の最大化を指向して各状態遷移における制御信号のドントケ

ア(Don't care : X)に論理値を割当てる手法が提案されている. しかしながら, 全状態遷移においてもテストされる観測点集合が同じであるために識別することができないハードウェア要素ペアが存在する.

一般的に, RTL で入力信号線数が 2 のべき乗でないマルチプレクサの制御信号値には選択すべき入力信号線が RTL の段階で決まっていないものが存在する. つまり, 入力信号線数が 2 のべき乗でないマルチプレクサには設計の自由度が存在する. それゆえ, 本手法では前述の識別可能ハードウェア要素ペア数の増加を目的として, RTL で記述されていないマルチプレクサの制御信号値に対して, RTL データパス中の信号線から分岐させた新たな入力信号線を追加し, マルチプレクサの入力数を 2 のべき乗に拡張する. さらに, そのマルチプレクサ設計において, ランダム入力選択方式と分解能向上入力選択方式の二つの識別可能故障ペア推定数を評価する.

本論文の構成は以下のとおりである. 第 2 章では本論文における前提知識について説明する. また, 第 3 章ではマルチプレクサの入力信号線選択に対する条件を示す. 第 4 章では診断容易化設計に用いるマルチプレクサの入力信号線選択の例を示す. 第 5 章ではランダム入力信号線選択アルゴリズムを示す. 第 6 章では実験結果を示し, 第 7 章ではまとめと今後の課題について述べる.

### 2. 前提知識

#### 2.1 RTL 回路

本論文で対象としている RTL 回路は演算を実行するデータパスとデータパスの制御を行うコントローラに分割して設計される. データパスとコントローラは, データパスからコントローラへの状態信号線と, コントローラからデータパスへ

A Consideration on Improvement of Fault Diagnostic Resolution by Control-Point Insertion Using Multiplexer Default Inputs

YEONGKYEONG YUN, Toshinori HOSOKAWA

の制御信号線で相互に接続されている。また、フルスキアン設計が適用されている。

## 2.2 デフォルトの制御信号値

入力信号線数が 2 のべき乗でないマルチプレクサの制御信号値には、対応する入力信号線が RTL の段階で決定されていないものが存在する。そのような制御信号値をデフォルトの制御信号値と定義する。また、本論文ではデフォルト制御信号値を持つマルチプレクサを設計対象とする。

## 2.3 ハードウェア要素

本論文では、データパスの信号線および制御信号線の故障をハードウェア要素と定義する。また、ハードウェア要素には識別可能ペアと識別不能ペアが存在し、ハードウェア要素ペアを以下の 4 つのタイプに分類する。

- type 1 (識別可能) : 少なくとも 1 つの状態遷移で  $f_i, f_j$  はともにテスト可能で、 $\text{Obs}(f_i) \neq \text{Obs}(f_j)$  である。

- type 2 (識別可能) : type1 以外で、少なくとも 1 つの状態遷移で、一方のみテスト可能、もう一方はテスト不能である。

- type 3 (識別不能) : type1, 2 以外で、少なくとも 1 つの状態遷移で、 $f_i, f_j$  はともにテスト可能で、 $\text{Obs}(f_i) = \text{Obs}(f_j)$  である。

- type 4 (識別不能) : 全状態遷移において  $f_i, f_j$  はともにテスト不能である。

本論文では、type1 と type2 を RTL における識別可能ペア、type3 と type4 を RTL における識別不能ペアという。また、2 つのハードウェア要素  $f_i, f_j$  の識別可能性は、テスト可能・不可能および観測点集合が異なるかどうかで判定する。 $\text{Obs}(f)$  は故障  $f$  の観測点集合である。この基準に基づき、ハードウェア要素ペア  $(f_i, f_j)$  を 4 つのタイプに分類する。また、type3 のハードウェア要素ペアに関しては、RTL では識別不能だが、ゲートレベルでそのハードウェア要素に対応する平均 95% 程度の故障が識別可能となる可能性がある。本論文では type3 のペアに着目して type1 または type1 に変化させるようなマルチプレクサの設計を行う。

## 2.4 識別可能故障ペア推定数

識別可能故障ペア推定数[6]とは、RTL 回路に対する構造的記号シミュレーション[5]の結果を用いて計算されたゲートレベルにおける識別可

能故障ペアの推定数である。この値は、実際のゲートレベル回路における分解能と高い相関関係にあることが文献[6]によって示されており、高い推定数の割合は分解能が高いことを表している。

## 3. マルチプレクサの入力信号線選択に対する条件

本章では、診断容易化設計において、マルチプレクサの新たな入力信号線として選択されるデータパス中の信号線候補について説明する。選択された入力信号線は分岐後、入力数が 2 のべき乗でない対象マルチプレクサの新たな入力として接続する。また、信号線候補は以下の条件 3 つをすべて満たすものとする。

### ● 条件 1 : 候補の種類

候補として選択可能な信号線は、モジュールの出力ポート、外部入力の出力ポート、マルチプレクサの入力ポートである。

### ● 条件 2 : 自己ループの禁止

候補として選択された信号線は対象マルチプレクサに追加接続後も回路内で自己ループを形成しない。すなわち、対象マルチプレクサの出力経路上の信号線を選択しない。

### ● 条件 3 : 選択回数

あるマルチプレクサの入力信号線として選択された信号線は、他のマルチプレクサの入力信号線として選択されない。

## 4. 診断容易化設計に用いる信号線選択

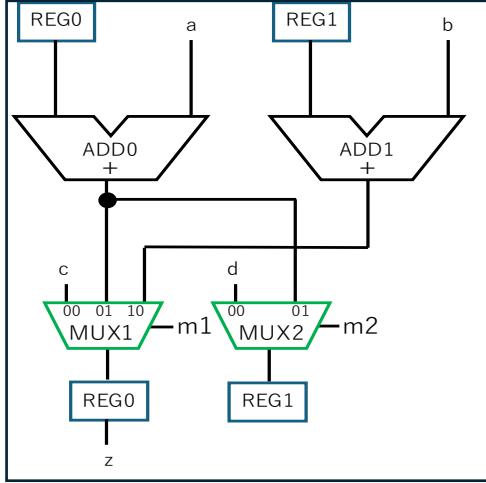

本章では、図 1 に示したデータパスを例に、マルチプレクサの設計変更について説明する。

図 1において、a, b, c, d は外部入力、z は外部出力、REG0, REG1 はレジスタ、ADD0, ADD1 は加算器、MUX1, MUX2 はマルチプレクサであり、m1, m2 は MUX1, MUX2 のそれぞれの制御信号線を表している。また、マルチプレクサの入力信号線の下の数字はその入力信号線を選択する制御信号値を表し、制御信号線に該当値が入力されるとその入力信号線が選択される。

この例において、入力信号線数が 2 のべき乗でない対象マルチプレクサは MUX1 である。MUX1 の入力信号線数は 3 であり、m1 は 2 ビットで表現できる 00, 01, 10, 11 の 4 つのうち、00, 01, 10 の 3 つがすでに使用されている。よって、デフォルト制御信号値は 11 である。また、デフォ

図 1. RTL のデータパス

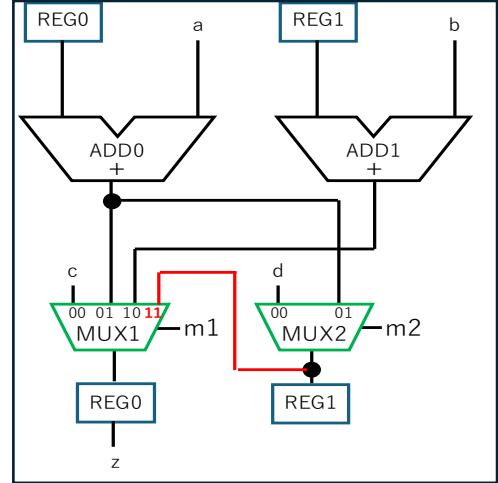

ルト制御信号値に対する入力信号線を決定した例を図 2 に示す。図 2 は、図 1 のデータパスから MUX2 の出力信号線を分岐させて MUX1 の新たな入力信号線として接続した例である。設計変更前は MUX2 の観測点が REG1 のみであるが、設計変更により REG0, REG1 の 2 つに増加したため、type3 であった一部の識別不能ハードウェア要素ペアが type1 の識別可能ハードウェア要素ペアに変化する可能性が向上する。

## 5. ランダム入力選択アルゴリズム

本章では、第 3 章で説明した信号線候補集合からランダムに信号線を選択するアルゴリズムを説明する。図 3 にランダム入力選択アルゴリズムを示す。入力はモジュール集合 M, RTL データパス D, 入力数が 2 のべき乗でない対象マルチプレクサ集合 TM である。出力は対象マルチプレクサに対して選択された入力信号線集合 MUX\_signal\_set, 候補信号線、マルチプレクサ、デフォルト入力ポートからなるトリプレットを要素とする集

図 2. 設計変更後のデータパス

合 SELECTED\_SIGNAL である。また、DF\_MUX はマルチプレクサのデフォルト入力数、cand は候補信号線を表す。まず、SELECTED\_SIGNAL を空集合に初期化する(4 行目)。次に、各対象マルチプレクサに対して、そのデフォルト入力数分だけ繰り返し、候補信号をランダムに信号線を選択する(5-7 行目)。選択された信号線が第 3 章で説明した条件をすべて満たすかを確認し、満たす場合のみ次の処理に進む(8-9 行目)。選択した候補を SELECTED\_SIGNAL とする(10 行目)。これにより j 番目の対象 MUX のデフォルト入力ポートに対して候補信号 cand が決定される。次に、同じ信号を以降の選択で再選択されないために M から cand を除外する(11 行目)。最後に、選択した信号線 SELECTED\_SIGNAL を返す(15 行目)。

## 5. 実験結果

本章では、RTL ベンチマーク回路 ex2 を対象とした実験結果を示す。表 1 に ex2 回路の回路情報を示す。左から状態遷移数、状態数、外部入力数、外部出力数、レジスタ数、演算器数、全ハードウェア要素数、MUX 数、入力信号線数が 2 のべき乗ではない対象 MUX 数である。表 2 は RTL における識別可能率、全ハードウェア要素ペアに占める type3 ペアの割合、識別可能故障ペア推定数[6]の 3 つの評価指標を示す。また、本実験で使用したコントローラは診断用 X 割当てが適用されたコントローラである。オリジナルは診断容易化設計を行う前のオリジナル回路を用いた実験結果である。ランダムは第 5 章で提案したランダム入力選択アルゴリズムを用いて入力信号線を選

---

**Algorithm**

1. Input : RTL Module-set M, Data-path D, Target mux set TM

2. Output : MUX-signal set, SELECTED\_SIGNAL

3. Design\_MUX (M, D, TM) {

4. SELECTED\_SIGNAL ←  $\emptyset$

5. for each MUX  $\in$  TM do

6. for  $(j = 0; j < |DF_MUX|; j++)$  {

7. cand ← RandSignal(M);

8. if (check\_rules (cand, MUX, j, D) == NG)

continue;

9. SELECTED\_SIGNAL = SELECTED\_SIGNAL  $\cup$  { (cand, MUX, j) }

10. M = M - { cand };

11. else

12. }

13. }

14. }

15. return SELECTED\_SIGNAL

図 3. ランダム入力選択アルゴリズム

表 1. ex2 の回路情報

| 回路名 | 状態遷移数 | 状態数 | 外部入力数 | 外部出力数 | レジスタ数 | 演算器数 | 全ハードウェア要素数 | MUX数 | 設計変更対象 MUX数 |

|-----|-------|-----|-------|-------|-------|------|------------|------|-------------|

| ex2 | 6     | 6   | 5     | 1     | 5     | 3    | 93         | 9    | 3           |

表 2. 設計変更後の結果

|            | オリジナル     | ランダム      | 分解能向上指向   |

|------------|-----------|-----------|-----------|

| 識別可能率[%]   | 99.862    | 99.857    | 99.975    |

| type3割合[%] | 1.778     | 2.084     | 1.587     |

| 推定数        | 406144160 | 450476844 | 451007844 |

択し, MUX に接続する 4 回の独立試行の平均値を表している. 分解能向上指向はデータバスの回路図を参考に type3 ペアから type1 ペアへの変化が期待できるような設計を手動で行った. 可能な限り, 入力数が 2 のべき乗でない MUX の出力信号線を優先に選択して対象 MUX の新たな入力信号線に追加する設計を行った. その結果, RTL における識別可能率は, オリジナル回路では 99.862%, ランダムは平均 99.857% であり, 分解能向上指向は 99.975% で一番識別可能率が高い結果となった. また, type3 ペアの割合も分解能向上指向設計が 1.587% で最小であった. 識別可能故障ペア推定数も分解能向上指向設計が 451007844 と最大で期待通りの結果となった. 表 2 からマルチプレクサの設計変更により RTL における故障ペアの識別可能率が向上することがわかる. また, 識別可能故障ペア推定数も最大 44863684 増加したことからゲートレベルに回路における分解能が高いことが期待される.

## 6.まとめと今後の課題

本論文では, マルチプレクサのデフォルト制御信号値に対応する入力信号線が明記されていないもの, すなわち入力数が 2 のべき乗でないマルチプレクサを対象に, データバス中の信号線から分岐して新たな入力信号線を追加する診断容易化設計手法を提案した. RTL ベンチマーク回路 ex2 による実験により, 本手法が RTL における識別可能率を向上させることがわかった.

今後の課題として, デフォルト制御の入力を用いた制御ポイント挿入のアルゴリズムを提案することが挙げられる.

## 参考文献

- [1] H. Y. Chang, E. Manning, and G. Metze: "Fault diagnosis of Digital Systems," John Wiley & Sons, Inc. 1970.

- [2] 藤田昌宏, "VLSI 設計工学 SoC における設計からハードウェアまで", 数理工学社, 2009.

- [3] 藤原秀雄, "デジタルシステムの設計とテスト", 工学図書株式会社, 2004.

- [4] 大塚裕衣, 細川利典, 吉村正義, 山崎 浩二, "識別可能重み付きハードウェア要素ペア数最大化のためのコントローラの制御信号のドントケア割当て法," 信学技報, vol. 123, no. 146, DC2023-12, pp. 25-30, August 2023.

- [5] K. Tsuchibuchi, T. Hosokawa and K. Yamazaki, "A Don't Care Filling Method of Control Signals for Controllers to Enhance Fault Diagnosability at Register Transfer Level," 22nd Workshop on RTL and High Level Testing, 2021.

- [6] 大塚裕衣, 細川利典, 吉村正義, 山崎 浩二, "レジスタ転送レベルにおける識別可能故障ペア推定数最大化のための状態遷移のドントケア割当て手法," DA シンポジウム, pp. 147-154, August 2024.

- [7] I. Pomeranz, S. Venkataraman and S. M. Reddy, "Z-DFD:design-for-diagnosability based on the concept of Z-detection," Int. Conf. on Test, 2004.

- [8] S. Udar and D. Kagaris, "Minimizing Observation Points for Fault Location," 24th IEEE Int. Symp. Defect and Fault Tolerance in VLSI Systems, 2009.

- [9] T. Aono, T. Hosokawa, M. Yoshimura, K. Yamazaki and M. Arai, "PBO-Based Pattern Replacement for Compacting Diagnostic Patterns to Achieve Complete Diagnostic Resolution," in IEEE International Symp. on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), 2025.