# 完全診断分解能テスト集合圧縮のためのツーバイワンアルゴリズム

日大生産工(院) ○青野 竜弥

京産大 吉村 正義

日大生産工 細川 利典

明治大 山崎 浩二

日大生産工 新井 雅之

## 1. まえがき

半導体微細化技術の進歩に伴い、超大規模集積回路 (Very Large Scale Integrated Circuits: VLSI) において、異常動作の物理的な原因を特定する故障解析は、歩留まり向上のために重要な。故障解析のコスト低減のために、故障 VLSI に存在する可能性のある故障 (被疑故障) を事前に絞り込んでおく故障診断[1]が重要である。故障診断を実行することで故障 VLSI の異常な外部出力応答を裏付けることのできる故障箇所を推定する。このとき、VLSI のテストに使用されたテスト集合において、識別可能な故障ペア数が多いほど、被疑故障数を削減することができる。しかしながら、故障検出を指向した手法で生成されたテスト集合では故障ペアの識別が考慮されていないため、故障ペアの識別が不十分な場合がある[2]。

テスト集合の診断分解能を向上させる手法として、様々な診断パターン (Diagnostic Pattern: DP) 生成法が提案されている[2]-[6]。文献[3]-[6]では、テスト集合に追加する DP 数を削減するための DP 生成法が提案されているが、故障検出を指向したテスト集合には、診断分解能の向上に寄与していないテストパターンが含まれている[2]。

それゆえ、文献[2]ではテストパターン置換法が提案されている。本手法は、診断分解能向上に比較的寄与していないテストパターンを、故障検出効率を維持しながら診断分解能が向上するテストパターンに置換することで、未識別な故障ペアを、テストパターン数を増加させないで識別する手法である。その結果、完全診断分解能を達成するために追加する DP 数が、従来手法に比べ削減している。しかしながら、追加した DP によって、各テストパターンの必須故障数[7]と必須識別故障ペア数[2]が変化したことによって、テストパターン数をさらに削減する余地があると考えられる。

本論文では、文献[2]の手法を用いて生成した完全故障検出効率と完全診断分解能を両立するテスト集合のテストパターン数を、ツーバ

イワンアルゴリズム[7] (Two by One: TBO) を用いて削減する。

## 2. 前提知識

本章では、本論文で取り扱う用語を定義する。

### 定義 1：テスト集合 $T$ の必須故障[7]

与えられたテスト集合  $T$  において、テストパターン  $t$  ( $\in T$ ) で検出可能な故障  $f$  が  $T$  中の  $t$  以外のテストパターンで検出不能であるとき、故障  $f$  をテスト集合  $T$  における  $t$  の必須故障という。

### 定義 2：識別可能な故障ペア[5]

テストパターン  $t$  で故障ペア  $(f_i, f_j)$  ( $f_i \neq f_j$ ) の 2 つの故障  $f_i, f_j$  の外部出力応答が異なるならば、故障ペア  $(f_i, f_j)$  は  $t$  で識別可能な故障ペアであるという。また、外部出力応答が一致するとき、故障ペア  $(f_i, f_j)$  は  $t$  で識別不能な故障ペアであるという。

### 定義 3：テスト集合 $T$ の必須識別故障ペア[2]

与えられたテスト集合  $T$  において、テストパターン  $t$  ( $\in T$ ) で識別可能な故障ペア  $(f_i, f_j)$  が  $T$  中の  $t$  以外のテストパターンで識別不能であるとき、故障ペア  $(f_i, f_j)$  をテスト集合  $T$  における  $t$  の必須識別故障ペアという。

## 3. 提案手法

本章では、縮退故障に対する完全故障検出効率と完全診断分解能を保持しながら、テストパターン数を削減するツーバイワンアルゴリズムについて説明する。本手法は、文献[7]で提案されているツーバイワンアルゴリズムを拡張し、完全故障検出効率と完全診断分解能を両立するテスト集合のテストパターン数を削減することを目的としている。そのために、テスト集合内の 2 つのテストパターンを、故障検出効率と診断分解能を維持するような 1 つのテストパターンに置換する手法を提案する。第3.1 節では充足割当問題について説明し、第3.2 節では複数目標故障テスト生成モデル、第3.3 節

A Two by One Algorithm for Compacting Test Set with Complete Diagnostic Resolution

Tatsuya AONO, Toshinori HOSOKAWA, Masayoshi YOSHIMURA, Koji YAMAZAKI and Masayuki ARAI

では複数故障ペア識別モデル、第3.4節では全体アルゴリズムについて説明する。

### 3.1 充足割当問題

充足割当問題(Satisfiability Problem: SAT)とは、論理和標準形 (Conjunctive Normal Form: CNF) の命題論理式が与えられたとき、それに含まれる変数の値を真または偽に定めることによって、命題論理式全体を真にできるか否かを判定する問題である。充足可能とは、命題論理式の論理変数の値を割当てた際に、式全体が真となる割当てを行うことである。充足不能とは、CNFの値を真にできる割当てが存在しないことである。

### 3.2 複数目標故障テスト生成モデル[8]

本節では、本手法における複数目標故障テスト生成モデルについて説明する。テスト集合の故障検出効率を維持するために、2つのテストパターン  $t_a, t_b$  の必須故障と2つのテストパターンのみで検出可能な故障を全て検出する必要がある。ある目標故障を検出するための制約は正常回路  $\emptyset_{GC}$ 、故障  $f_i$  の故障回路  $\emptyset_{f_i}$ 、故障  $f_i$  の検出判定回路  $\emptyset_{det}$  と故障励起制約  $\emptyset_{exc}$  で構成される。目標故障が複数存在する場合は、各故障に対応する故障回路、検出回路、故障励起制約が生成される。故障回路は故障  $f_i$  の故障箇所から到達可能な信号線で構成される。故障検出回路は、正常回路と故障回路の対応する外部出力を入力としてXOR演算を行うモデルを構築する。故障の影響はある1つの外部出力に伝搬すれば十分であるため、2つ以上のXOR演算の出力をOR演算し、OR演算の出力に1を割当てる。故障励起制約は、正常回路における故障箇所に対応する信号線に値を割当てる。対象故障が0縮退故障である場合、正常回路における故障箇所に1、1縮退故障である場合、正常回路における故障箇所に0を割当てる。

### 3.3 複数故障ペア識別モデル

本節では、本手法における複数目標故障ペア識別モデルについて説明する。テスト集合の故障検出効率を維持するために、2つのテストパターン  $t_a, t_b$  の必須識別故障ペアと2つのテストパターンでのみ識別可能な故障ペアを全て識別する必要がある。ある目標故障ペアを識別するための制約は、正常回路と故障  $f_i$  の故障回路と故障ペアの識別回路  $\emptyset_{dist}$  から構成される。正常回路と故障回路は3.2節と同様に構築する。識別回路は、故障ペアの各故障に対応する故障回路の外部出力同士をXOR演算で接続する。一方の故障のみ到達可能な外部出力が存在する場合、その故障回路の出力は正常回路とのXOR演算を行う。到達可能な外部出力が複数

存在する場合、XOR演算した結果を入力したOR演算を行う。また、故障ペアを識別するために、各故障回路の故障箇所に故障値、識別回路の出力に1を割当てる。

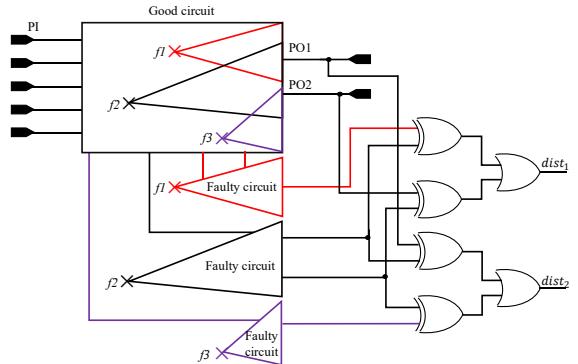

図1に、2つの故障ペア  $(f1, f2)$  と  $(f2, f3)$  の故障ペア識別モデルを示す。故障ペア  $(f1, f2)$ において、外部出力PO1は両故障が到達可能な外部出力であるため、故障回路の対応する外部出力同士をXOR演算する。一方、PO2は片方の故障のみ到達可能であるため、正常回路と対応する故障回路でXOR演算を行う。各故障ペアの識別回路の出力に1を割当て、各故障回路の故障箇所に故障値を割当てる。

2つのテストパターン  $t_a, t_b$  を1つのテストパターンに置換するテストパターン生成モデルを式(1)で定式化する。 $O$ はテストパターン  $t_a$  の必須故障数、 $P$ はテストパターン  $t_b$  の必須故障数、 $Q$ は  $t_a, t_b$  のみで検出可能な故障数、 $R$ は  $t_a$  の必須識別故障ペア数、 $S$ は  $t_b$  の必須識別故障ペア数、 $T$ は  $t_a, t_b$  のみで識別可能な故障ペア数である。 $\emptyset_{GC}$ 、 $\emptyset_{f_i}$ 、 $\emptyset_{det_j}$ 、 $\emptyset_{exc_j}$ 、 $\emptyset_{dist_k}$  は3.2節、3.3節と同様である。

$$\emptyset_{GC} \cdot \bigwedge_{i=1}^{R+S+T} \emptyset_{f_i} \cdot \bigwedge_{j=1}^{O+P+Q} (\emptyset_{det_j} \cdot \emptyset_{exc_j}) \cdot \bigwedge_{k=1}^{O+P+Q} \emptyset_{dist_k} = 1 \quad (1)$$

本手法では、各テストパターンのペアに対して式(1)で定式化し、式(1)を充足する変数割当てが存在する場合、生成されたテストパターンをテスト集合に追加し、対象となった2つのテストパターンを削除する。

### 3.4 全体アルゴリズム

図2に完全故障検出効率と完全診断分解能を両立するためのツーバイワンアルゴリズムの全体アルゴリズムを示す。入力は回路  $C$ 、初期テスト集合  $TS$ 、検出可能な代表故障集合  $F$ 、必須故障数の閾値  $THD$  である。

図1. 複数故障ペア識別モデル

```

Input: Circuit C, Test Set TS, Testable Collapsed Fault Set F, Threshold THD

Output: Test Set T

1.  $T' = \emptyset$ ;

2.  $ESSF = \text{Fault\_Simulation}(C, TS, F)$ ;

3.  $T' = \text{Select\_Target\_Test\_Pattern}(TS, ESSF, THD)$ ;

4.  $T = TS - T'$ ;

5.  $ESSFP = \text{Diagnostic\_Simulation}(C, T, T', F)$ ;

6. For each unmarked target test pattern  $t1$  in  $T'$

7. {

8.   For each unmarked target test pattern  $t2$  ( $\neq t1$ ) in  $T'$

9.   {

10.      $tp = \text{Test\_Generation}(C, t1, t2, ESSF, ESSFP)$ ;

11.     if ( $tp \neq \text{NULL}$ )

12.     {

13.        $T = T \cup tp$ ;

14.       mark  $t1$  and  $t2$ ;

15.       perform fault simulation with  $tp$  and update  $ESSF$  and  $ESSFP$ ;

16.     }

17.   }

18. }

19. add the unmarked test patterns of  $T'$  to  $T$ ;

20. return  $T$ ;

```

図2. 全体アルゴリズム

まず、対象テストパターン集合 $T$ を初期化する(1行目). 次に、故障シミュレーションを実行し、各テストパターンの必須故障を同定し、必須故障集合 $ESSF$ に格納する(2行目). 閾値 $THD$ と必須故障集合 $ESSF$ を基に、必須故障数が閾値以下のテストパターンを $T'$ に格納する(3行目). 初期テスト集合のテストパターンの内、対象テストパターン以外のテストパターンを最終テスト集合 $T$ に格納する(4行目). 次に $T$ に含まれる各テストパターンで識別可能な故障ペアを削除しながら、 $T'$ に含まれる各テストパターンの必須識別故障ペアを同定し、(5行目)必須識別故障ペア集合 $ESSFP$ に格納する. $T'$ の中から置換されていない2つのテストパターン $t1$ と $t2$ を選択し(6, 8行目), 2つのテストパターンを置換するためのテストパターン生成を試みる(10~15行目). テストパターン $t1, t2$ に対して式(1)を用いて定式化し、ソルバー

を用いてテストパターン生成を行う(10行目). テストパターンが生成可能であった場合、生成されたテストパターンを最終テスト集合 $T$ に追加し(13行目), テストパターン $t1$ と $t2$ をマークし、ツーバイワンアルゴリズムの対象外とする(14行目). 生成されたテストパターンに対して故障シミュレーションを実行し、生成されたテストパターンで検出された必須故障、必須識別故障ペアをそれぞれ $ESSF, ESSFP$ から削除する(15行目). 最後に $T'$ 中のマークされていないテストパターンを最終テストパターン $T$ に追加し(19行目), テスト集合 $T$ を出力する(20行目).

#### 4 実験結果

提案手法はC言語で実装し、フルスキャン設計を仮定したISCAS' 89ベンチマーク回路とITC' 99ベンチマーク回路を対象に実験した. 計算機としてCorei9 13900 (3.0GHz) および32GBメモリを搭載したコンピュータを用いた. 本手法では、SATソルバーとしてclasp[9]を使用した. claspのバージョンは3.3.9である. 1テスト生成当たりのclaspの制限時間は300秒、閾値を必須故障数の平均値に設定した. 文献[2]の手法で生成した. 完全故障検出効率と完全診断分解能を両立するテスト集合を初期テスト集合とした.

表1に提案手法の適用結果を示す. Circuitは回路名を示している. #Faultは、検出可能な代表故障数を示している. #Target Patternsはツーバイワン対象テストパターン数を示している. #Test Sizeはテスト集合のテストパターン

表1. 実験結果

| Circuit | #Fault | #Target Patterns | #Test Size |       | Reduction Ratio[%] | CPU Time[s] |

|---------|--------|------------------|------------|-------|--------------------|-------------|

|         |        |                  | Init.      | Prop. |                    |             |

| s5378   | 4,511  | 85               | 136        | 116   | 14.7               | 21.6        |

| s9234   | 6,475  | 105              | 178        | 152   | 14.6               | 194.3       |

| s13207  | 9,512  | 180              | 250        | 246   | 1.6                | 85.8        |

| s15850  | 11,308 | 76               | 124        | 122   | 1.6                | 62.0        |

| s35932  | 34,534 | 18               | 28         | 22    | 21.4               | 60.1        |

| s38417  | 30,579 | 45               | 91         | 81    | 11.0               | 71.4        |

| s38584  | 34,489 | 78               | 133        | 123   | 7.5                | 501.8       |

| b15     | 21,261 | 268              | 436        | 430   | 1.6                | 2298.2      |

| b20     | 45,140 | 499              | 787        | 749   | 4.8                | 4144.6      |

| b21     | 45,776 | 517              | 811        | 777   | 4.2                | 2041.3      |

| b22     | 67,192 | 420              | 677        | 663   | 2.1                | 2476.4      |

数を示し, Init. は初期テスト集合, Prop. は提案手法適用後のテストパターン数を示している. Reduction Ratio は提案手法によるテストパターン数の削減率を示し, CPU Time は実行時間を示している.

ツーバイワンアルゴリズムを適用した結果, テストパターン数を文献[2]に比べ, 平均5.1% 削減した. 実験結果より, すべての回路で文献[2]で生成されたテスト集合のテストパターン数よりもテストパターン数を削減した. これは文献[2]で, テストパターン置換で識別されなかつた未識別故障ペアに対して診断用パターンを生成し, 追加したことにより, 各テストパターンの必須故障数や必須識別故障ペア数が変化した結果, テストパターン数を削減する余地が生まれたことが要因であると考えられる.

## 5 まとめと今後の課題

本論文では, ツーバイワンアルゴリズムを用いた完全故障検出効率と完全診断分解能を両立するテスト集合の圧縮法を提案した. ISCAS' 89 と ITC' 99 での実験では, テストパターン数を文献[2]に比べ平均5.1% 削減した. 今後の課題として, Mバイワンアルゴリズムへの拡張が挙げられる.

## 参考文献

- [1] H. Y. Chang, E. Manning and G. Metze, *Fault Diagnosis of Digital Systems*. John Wiley & Sons, 1970.

- [2] T. Aono, T. Hosokawa, M. Yoshimura, K. Yamazaki and M. Arai, "PBO-Based Pattern Replacement for Compacting Diagnostic Patterns to Achieve Complete Diagnostic Resolution," in IEEE International Symp. On Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), 2025.

- [3] C. H. Wu, K. J. Lee and S. M. Reddy, "An Efficient Diagnosis-Aware ATPG Procedure to Enhance Diagnosis Resolution and Test Compaction, " in IEEE Trans. on Very Large-Scale Integration (VLSI) Syst., 2019, pp.2105-2118.

- [4] J. Ye, X. Zhang, Y. Hu and X. Li, "Substantial Fault Pair At-a-Time (SFPAT): An Automatic Diagnostic Pattern Generation Method, " in 19th IEEE Asian Test Symp., 2010, pp.192-197.

- [5] Y. Zhang and V. D. Agrawal, "Reduced complexity of test generation algorithms for transition fault diagnosis," in Proc. Int. Conf. Comput. Design, 2011, pp. 96–101.

- [6] K. J. Lee, C. H. Wu and T. Y. Hou, "An Efficient Procedure to Generate Highly Compact Diagnosis Patterns for Transition Faults," in IEEE Trans on Computer-Aided Design of Integr. Circuits. Syst., 2022, pp. 737-749.

- [7] S. Kajihara, I. Pomeranz, K. Kinoshita and S. M. Reddy, "On Compacting Test Sets by Addition and Removal of Test Vectors," in Proc of IEEE VLSI Test Symposium, 1994, pp. 202-207.

- [8] T. Hosokawa, M. Mizota, M. Yoshimura and M. Arai, "A Low Power Oriented Multiple Target Test Generation Method for 2-Cycle Gate-Exhaustive Faults," in IEEE Int. Symp. on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), 2024, pp. 1-6.

- [9] M. Gebser, B. Kaufmann, A. Neumann, and T. Schaub, "Conflict-Driven answer set solving," Artificial Intelligence, vol.187-188, pp.52–89, 2012.