## 2 サイクルゲート網羅微小遅延故障のテスト生成のための

### 有効故障伝搬経路集合の評価

日大生産工(院) ○日向野 隼多 日大生産工 細川 利典

京産大 吉村 正義 日大生産工 新井 雅之

#### 1. まえがき

近年、半導体集積技術の発展に伴い、設計される超大規模集積回路(Very Large Scale Integrated circuits: VLSI)の大規模化・複雑化、高速化が急速に進展している。また、それに伴い不良 VLSI にはセルや信号線に物理的欠陥が存在し、論理回路においても論理機能が故障により別な論理機能に変化する論理故障や本来の実動作速度でテストした場合に誤った動作をするタイミング故障など様々な故障が存在する[1]。したがって、信号線における欠陥に加え、セル内の欠陥も増加している。

セル内のタイミング欠陥はレイアウト解析をおこなうことで、欠陥が存在するセルに対してどの入力系列でセルの出力信号線に故障励起可能か否かを判断する。セル内のタイミング欠陥の位置やタイプによっては特定の入力系列でのみ故障励起可能な場合があり、遷移故障などの基本的な故障モデルに対するテスト集合では検出されない場合がある[2]。つまり、セル内の欠陥は縮退故障モデルなどに比べ検出が困難である。したがって、テスト時にセル内の欠陥を見逃す可能性があり、不良 VLSI を良品と判断するテストエスケープを引き起こす可能性がある[2]。

本論文では、セル内のタイミング欠陥によりセルの出力信号線の値が遷移する際に遅延が発生する故障に着目する。セルの出力信号線に遷移を発生させるセルの各 2 パターンの組合せに対して、その遷移が遅延する故障モデルを 2 サイクルゲート網羅故障と呼ぶ[3]。2 サイクルゲート網羅故障を検出するテストベクトルはセルのタイミング欠陥を検出できる。文献[4]では、2 サイクルゲート網羅故障に対する低消費電力指向複数目標故障テスト生成手法が提案され、動的テスト圧縮[5]を用いて生成されたテストベクトルは指定された WSA[6]以下のキャプチャセーフテストベクトルであることが報告されている。

しかしながら、2 サイクルゲート網羅故障モデルは、セルの出力に生じた遅延値が十分に大きいと考えられたモデルである。そのため、セル内のタイミング欠陥により生じた出力の遅延値が小さい場合は、例え 2 サ

イクルゲート網羅故障を全て検出できるテスト集合を生成したとしても、そのようなセル内タイミング欠陥をもつ VLSI を不良品と判断できない可能性がある。また、2 サイクルゲート網羅故障数はゲート数とゲートの入力数に依存するため、大規模回路になるにつれ、故障数やテストベクトル数が増大する可能性がある。信号線に対する微小遅延故障[7]や抵抗性オープン故障[8-10]、抵抗性ブリッジ故障[1]に起因する微小遅延故障のテスト生成手法は数多く提案されているが、セル内の欠陥に起因して発生する微小遅延故障については提案されていない。したがって、セル内の微小なタイミング欠陥を精度よくモデル化した故障モデルとそれに対するテスト生成手法の提案が重要となる。

本論文では、セル内タイミング欠陥を低コストかつ高精度でテストするために、2 サイクルゲート網羅微小遅延故障モデルを提案し、そのテスト生成に使用するための有効故障伝搬経路の列挙について説明し、その割合を評価する。

なお本論文は、トランジスタ回路上の説明にはセル、デジタル回路上の説明にはゲートと呼ぶ。

本論文の構成は以下のとおりである。第 2 章では、2 サイクルゲート網羅故障モデルについて説明し、第 3 章では、2 サイクルゲート網羅微小遅延故障について説明する。第 4 章では、有効故障伝搬経路の列挙について説明し、第 5 章では、実験結果を示す。最後に第 6 章でまとめと今後の課題について説明する。

#### 2. 2 サイクルゲート網羅故障モデル

本章では、2 サイクルゲート網羅故障モデルについて説明する。

2 サイクルゲート網羅故障は、あるゲートの出力信号線に遷移を発生させるそのゲートの入力への各 2 パターンの組合せに対して、その遷移の遅延を引き起こす故障である。2 サイクルゲート網羅故障モデルは、セル内のタイミング欠陥によりセルの出力信号線の値が遷移する際に遅延が発生する故障を網羅する。

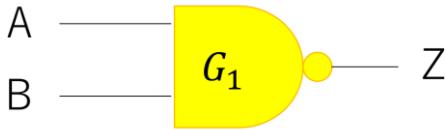

図1の2入力NANDの2サイクルゲート網羅故障集合を表1に示す。出力信号線の値が遷移する場合の入力へ

---

Evaluation of Effective Fault Propagation Path Sets for Test Generation

of Two-Cycle Gate Exhaustive Small Delay Faults

Hayata HIGANO, Toshinori HOSOKAWA,

Masayoshi YOSHIMURA and Masayuki ARAI

図 1. 2 入力 NAND ゲート例

の 2 パターンの組合せにおいて故障を定義するため, ゲートの入力数を  $n$  とした場合, 2 サイクルゲート網羅故障数は  $2 \times (2^n - 1)$  個となる. ただし, 2 入力 EXOR (EXNOR) ゲートの場合は  $2^2 \times 2 = 8$  個である. 表 1 の 2 サイクルゲート網羅故障数は  $2 \times (2^2 - 1) = 6$  個である.  $f_1$  から  $f_3$  は, 出力信号線が 0 から 1 に立上り遷移する時間が遅延した故障であり,  $f_4$  から  $f_6$  は, 出力信号線が 1 から 0 に立下り遷移する時間が遅延した故障である. また, 各ゲートの 2 サイクルゲート網羅故障集合は同一のテストベクトルでは検出されない独立故障集合 [4] である.

### 3. 2 サイクルゲート網羅微小遅延故障モデル

本章では, 2 サイクルゲート網羅微小遅延故障モデルを提案する.

表 1. 2 入力 AND ゲートにおける

2 サイクルゲート網羅故障集合

| Fault ID | Input |   |       |   | Output      |       |

|----------|-------|---|-------|---|-------------|-------|

|          | 1 時刻目 |   | 2 時刻目 |   | 1 時刻目       | 2 時刻目 |

|          | A     | B | A     | B | Z (正常値/故障値) |       |

| $f_1$    | 0     | 0 | 1     | 1 |             |       |

| $f_2$    | 0     | 1 | 1     | 1 | 1           | 0/1   |

| $f_3$    | 1     | 0 | 1     | 1 |             |       |

| $f_4$    | 1     | 1 | 0     | 0 |             |       |

| $f_5$    | 1     | 1 | 0     | 1 | 0           | 1/0   |

| $f_6$    | 1     | 1 | 1     | 0 |             |       |

2 サイクルゲート網羅故障モデルは遅延サイズを持たず, どの故障伝搬経路を伝搬してもクロック周期間に間に合わせに, その故障は検出できる. しかしながら, 実際のセル内部のタイミング欠陥によるセルの出力における遅延サイズが小さい場合, 信号伝搬時間が短い経路に沿って故障の影響を伝搬してテストベクトルを生成した場合, そのテストベクトルでは, そのセル内部のタイミング欠陥は検出できないという問題点がある.

2 サイクルゲート網羅故障微小遅延故障モデルは, 出力の遷移が遅延サイズ( $\Delta$ )を持つ. 図 1 の 2 入力 NAND の 2 サイクルゲート網羅微小遅延故障モデルを以下のように表記する.

$(G_1, A \text{ の入力系列}, B \text{ の入力系列}, Z \text{ の出力系列}, \Delta)$

例えば, 図 1 の 2 入力 NAND ゲート  $G_1$  の入力に  $(A \text{ 入力の信号系列}, B \text{ 入力の信号系列}) = (11, 01)$  を印加した時, 出力の立上り遷移が 3 ユニット遅延する 2 サイクルゲート網羅故障を  $(G_1, 11, 01, 10/1, \Delta 3)$  と表記する. (01) は 1 時刻目の信号値が 0, 2 時刻目の信号値が 1 であることを示す. 出力信号系列の 2 時刻目の 0/1 は故障がない場合の信号値が 1, 故障がある場合の信号値が 0 であることを示す.

### 4. 有効故障伝搬経路の列挙

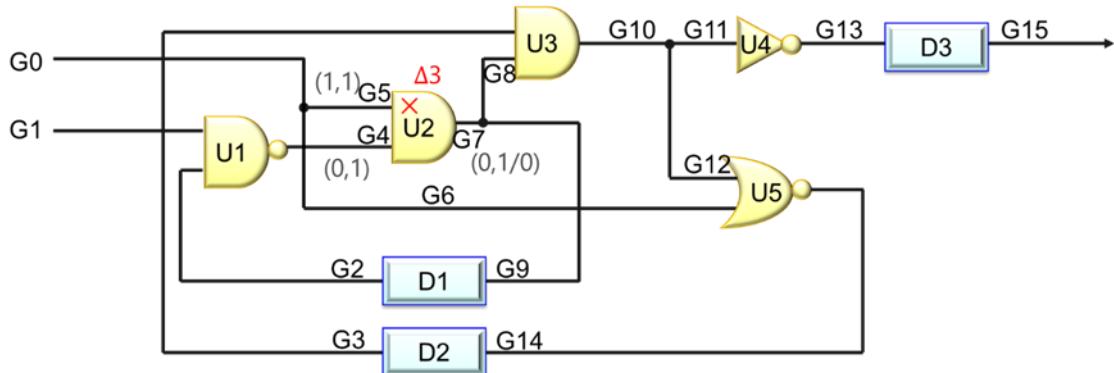

本章では有効故障伝搬経路の列挙について説明する. 図 2 に故障  $(U_2, 11, 01, 01/0, \Delta 3)$  の有効故障伝搬経路の列挙の例を示す. 信号線の配線遅延は 1 ユニットとし, セルの遅延はセルの入力数とする. また, 図 2 におけるクロック周期は 16 ユニットに設定されている, このとき, 外部入力および FF から故障箇所までの信号伝搬時間は  $G_2 \rightarrow G_4$  の経路で最長 6 ユニットとなる. 故障箇所の出力から観測点である FF までの経路は, 信号伝搬時間が 2 ユニットである  $G_7 \rightarrow G_9$  の経路 1,

図 2. 故障  $(U_2, 11, 01, 01/0, \Delta 3)$  の有効故障伝搬経路の列挙例

表 2. 各回路における有効故障伝搬経路

| 回路名  | 故障数  | クロック周期 | 遅延サイズ | 故障伝搬経路数 | 各ゲートにおける有効故障伝搬経路数 |    |      | 各ゲートにおける有効故障伝搬経路数の割合 (%) |    |      |

|------|------|--------|-------|---------|-------------------|----|------|--------------------------|----|------|

|      |      |        |       |         | 最大                | 最小 | 平均   | 最大                       | 最小 | 平均   |

| s27  | 52   | 27     | 3     | 124     | 12                | 0  | 9.3  | 100                      | 0  | 47.0 |

|      |      |        | 5     |         | 12                | 0  | 9.3  | 100                      | 0  | 47.0 |

|      |      |        | 10    |         | 24                | 0  | 12.6 | 100                      | 0  | 82.9 |

| s208 | 508  | 50     | 3     | 16733   | 72                | 0  | 18.4 | 100                      | 0  | 11.8 |

|      |      |        | 5     |         | 96                | 0  | 31.1 | 100                      | 0  | 19.9 |

|      |      |        | 10    |         | 144               | 0  | 51.9 | 100                      | 0  | 33.2 |

| s298 | 1056 | 36     | 3     | 3546    | 50                | 0  | 15.2 | 100                      | 0  | 43.5 |

|      |      |        | 5     |         | 66                | 0  | 21.0 | 100                      | 0  | 57.8 |

|      |      |        | 10    |         | 72                | 0  | 22.4 | 100                      | 0  | 64.1 |

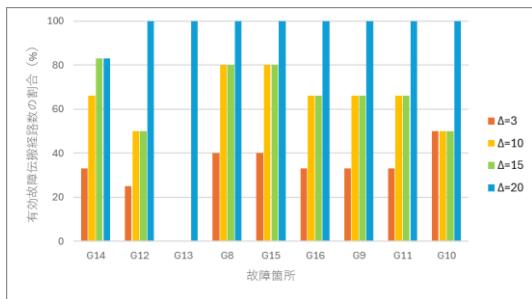

図 3. s27 の有効故障伝搬数の割合

8 ユニットである G7->G8->G10->G11->G13 の経路 2, 9 ユニットである G7->G8->G10->G12->G14 の経路 3 の 3 つが存在する。故障ゲートの遅延サイズが 3 ユニットであるため、経路 1 を伝搬した場合は、信号伝搬時間の合計値が 11 ユニットで故障が存在しても正常動作する。しかしながら、経路 2 や経路 3 を故障の影響が伝搬した場合、信号伝搬時間の合計値はそれぞれ 17 および 18 となり、故障を検出することができる。経路 2 や経路 3 のように故障が検出可能である経路を有効故障伝搬経路と呼ぶ。

列挙した有効故障伝搬経路はテスト生成モデルに追加する。このとき、経路 3 のように信号伝搬時間が長い経路を優先して故障伝搬されるようにテスト生成をする。これは、実際にセル内タイミング欠陥によって引き起こされる遅延サイズがより小さい場合を考えし、より信号伝搬時間の長い経路を選択することで実際の欠陥 VLSI をより多く検出できる可能性が高まるためである。

## 5. 実験結果

本章では、実験結果について説明する。提案手法は C 言語で実装され、Core i7-13700, 16GB メモリ搭載の PC を用いて実験をおこなった。対象回路は ISCAS' 89 ベンチマーク回路である。

表 2 に実験結果を示す。s27, s208, 298 の 3 回路

に対して遅延サイズが 3 ユニット、5 ユニット、10 ユニットの故障を仮定した時の故障伝搬経路を解析した。

表 2 から、各回路においてクロック周期が長いと故障伝搬経路数が多くなることが分かる。したがって、故障箇所を通過するパスが長いほど故障伝搬経路数が多くなることが考えられる。また、s208 のようにクロック周期が長い、すなわち故障伝搬経路数が多い回路程、各ゲートにおける有効故障伝搬経路数の割合が小さいことが分かる。これは、クロック周期が長い回路におけるパス長が比較的長くなるため、4 章の経路 1 のような信号伝搬時間がクロック周期内に収まり正常動作してしまうパスの割合が高くなることが原因であると考えられる。

図 3 は s27 回路の各ゲートにおいて、遅延サイズを設定した際のそのゲートを通る故障伝搬経路の内、遅延値がクロック周期以上となった有効故障伝搬経路の数を示したものである。

図 3 から、 $\Delta$ が 3 の時の有効故障伝搬経路数の割合は平均約 31.9% であることがわかる。また、 $\Delta$ が 10 の時の有効故障伝搬経路数の割合は平均約 31.9% であった。 $\Delta$ が 10 を超えるような遅延サイズが十分大きい場合と比較して、遅延サイズが小さい場合でも故障伝搬可能な経路は一定数存在しているが、割合が低いことが考察できる。

## 6. むすび

本論文では、2 サイクルゲート網羅微小遅延故障のテスト生成の研究に先駆けて、有効故障伝搬経路集合の例挙に関する評価をおこなった。

実験結果から、遅延サイズによる有効故障伝搬経路数の割合の変化を解析することができた。

今後の課題は、有効故障伝搬経路を活かした効率的な 2 サイクルゲート網羅微小遅延故障のテスト生成を提案することが挙げられる。

## 参考文献

- 1) 藤原秀, ディジタルシステムの設計とテスト, 工学図書株式会社, 東京, 2004, pp 135-135.

- 2) K.Y. Cho, S. Mitra, and E.J. McClusky, “Gate Exhaustive Testing”, IEEE International Conference on Test, Austin, USA, Nov. 2005, no.31.3, pp.1-7.

- 3) Irith Pomeranz, “Efficient Identification of Undetectable Two-Cycle Gate-Exhaustive Faults”, Proc.of IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, Volume:41 Issue 3.

- 4) T. Hosokawa, M. Mizota, M. Yoshimura, and M. Arai, “A Low Power Oriented Multiple Target Test Generation Method for 2-Cycle Gate-Exhaustive Faults,” IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Didcot, United Kingdom, Oct. 2024.

- 5) G. Tromp, “Minimal Test Sets for Combinational Circuits,” IEEE International Conference on Test, no.7.3, pp.204-209, Nashville, USA, Oct.1991.

- 6) A.Krstic, and K-T.Cheng, “Delay Fault Testing for VLSI Circuits,” Springer, 1998.

- 7) Sudhakar M. Ileddy, Irith Pomeranz and Seiji Kajihara, “On the effects of Test Compaction on Defect Coverage,” VLSI Test Symposium, pp.430-435. 1996.

- 8) Haluk Konuk, “Voltage- and Current-Based Fault Simulation for Interconnect Open Defects”, Computer-Aided Design of Integrated Circuits and Systems, pp.1768-1779, 1999.

- 9) James C. -M. Li, Chao-Wen Tseng, and E.J. McCluskey, “Testing for Resistive Opens and Stuck Opens”, Test Conference, pp.1049-1058, 2001.

- 10) Yoshinobu Higami, Hiroshi Furutani, Takao Sakai, Shuichi Kameyama and Hiroshi Takahashi, “Test Pattern Selection for Defect-Aware Test”, Test Symposium, pp.102-107, 2011.