# 遷移故障検出率向上のための LOC テストに基づく

## コントローラ拡大法

日大生産工(院) ○竹内 勇希 日大生産工 細川 利典

日大生産工 山崎 紘史 京産大 吉村 正義

### 1.はじめに

近年、超大規模集積回路(Very Large Scale Integrated Circuits : VLSI)の微細化や高速化、電源電圧の低下にともない、縮退故障モデル[1]のテストだけでなく、遷移故障モデル[2]などのタイミング欠陥に対するテストが必要不可欠となっている[3]。タイミング欠陥に対する実速度スキャンテストとして、ブロードサイド方式[4]とスキュードロード方式[5]が提案されているが、設計の容易性の観点から、ブロードサイドテスト方式による実速度スキャンテスト[4]が広く採用されている。

しかしながら、ブロードサイドモデルを用いた遷移故障モデルのテスト生成では、回路構造に起因するテスト不能故障数が縮退故障と比較し、数多く存在する。そのため、構造テストという観点では現状の遷移故障検出率のテストでは不十分であり、潜在的なタイミング欠陥を見逃す可能性がある。したがって、テスト生成時において遷移故障モデルのテスト不能故障数を削減し、故障検出率を向上させることが重要である。

RTL回路をデータパスとコントローラに分けて設計した回路を対象に、面積や遅延のオーバーヘッドの増大を抑制するテスト容易化設計(Design for Testability:DFT)[6-8]手法として、コントローラ拡大[9-12]が提案されている。コントローラ拡大とは通常動作時では遷移し得ない無効状態[11]について、テスト時に動作する状態として設計する手法である。

文献[9,10]は非スキャンテストを対象としたコントローラ拡大を用いたDFT法である。文献[9]はRTLデータパスにおけるテストビリティ向上のためのコントローラ拡大を用いたDFT手法を提案している。また、文献[10]はコントローラ拡大を用いた、テスト容易化機能的時間展開モデル[10]の生成法について提案している。また、文献[11,12]はスキャンテストを対象としたコントローラ拡大を用いたDFT法であり、無効テスト状態[12]と演算器並列テスト[11]に必要な状態遷移を設計してコントローラ拡大を行うことでテストパターン数削減をする手法を提案している。文献[11]ではテストパターン数削減のためのスキャンテストに基づくテストポイント挿入とコントローラ拡大を用いた

RTLでのDFT法を提案している。文献[12]ではRTLデータパス内のハードウェア要素の並列テストを実現するためのコントローラ拡大法を提案している。

しかしながら、文献[11,12]は縮退故障モデルを対象としたDFT手法であり、遷移故障モデルを対象としたDFT手法に拡張する必要がある。また文献[11,12]はテストパターン数削減に焦点を当てたDFT手法であり、本論文では、遷移故障検出率の向上を目的としたDFT手法を提案する。

本論文では、文献[11,12]の手法を遷移故障モデルにおける故障検出率向上のためのDFT手法に変更し、データパス内のテスト不能なハードウェア要素(マルチプレクサ(Multiplexer:MUX)とレジスタ)をテスト可能にするコントローラ拡大法を提案する。

### 2. MUX のテストの故障検出率向上ための諸定義

#### 2.1 MUX のテストレジスタ

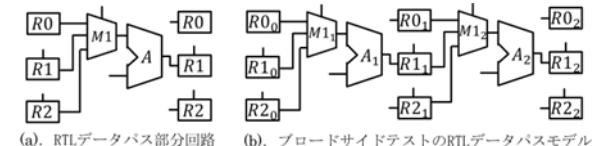

図1(a)にRTLデータパスの部分回路、図1(b)にRTLデータパスのブロードサイドテストにおけるテスト生成モデルを示す。

図1において、Aは演算器、R0～R2はレジスタ、M1はマルチプレクサを表す。また、R1、R2はホールド機能付レジスタである。マルチプレクサM1の入力信号線は下から順に入力00、入力01、入力10とし、制御値に対応する入力信号線の値がM1の出力信号線に出力される。また、図1(b)において、ハードウェア要素の右下の添え字は各時刻を示している。

ブロードサイドテストを用いた遷移故障のテストでは、1パターン目のテストパターンによって、1時刻目回路の故障信号線の値を初期化する。その後、2時刻目の回路を動作させる2パターン目のテストペー

(a). RTLデータバス部分回路 (b). ブロードサイドテストのRTLデータバスモデル

図1. RTLデータバス

A Controller Augmentation method based on LOC test for improve to transition fault coverage

Yuki TAKEUCHI, Toshinori HOSOKAWA, Hiroshi YAMAZAKI and Masayoshi YOSHIMURA

ンで故障信号線を励起・伝搬させ、故障影響をレジスタで観測する。

1 パターン目のテストパターンはシフト動作によってスキャン端子からレジスタに印加され、2 パターン目のテストパターンは1 パターン目のテストパターンに対する回路応答を利用する。

本論文では、 $MUX_j$  の入力  $i$  から入力方向に到達可能なレジスタを  $MUX_j$  の入力  $i$  の入力レジスタ[11]とする。また、 $MUX_j$  の出力から出力方向に到達可能なレジスタを  $MUX_j$  の出力レジスタ[11]とする。 $MUX_j$  の入力レジスタと  $MUX_j$  の出力レジスタを合わせて  $MUX_j$  のレジスタとする。

図 1(a)において、M1 の入力 00 から入力方向に到達可能なレジスタは R2、入力 01 から入力方向に到達可能なレジスタは R1、入力 10 から入力方向に到達可能なレジスタは R0 となる。また M1 の出力から出力方向に到達可能なレジスタは R1 となる。よって M1 の入力レジスタは R0,R1,R2、M1 の出力レジスタは R1 となる。

また、遷移故障モデルでの RTL データパス回路中のあるハードウェア要素のテスト実行中に 1 パターン目のテストパターンが印加されている  $MUX_j$  の入力  $i$  の入力レジスタを  $MUX_j$  の入力  $i$  の 1 パターン目テストレジスタとする。

また、2 パターン目のテストパターンが印加されている  $MUX_j$  の入力  $i$  の入力レジスタを  $MUX_j$  の入力  $i$  の 2 パターン目テストレジスタとする。

同様に  $MUX_j$  の入力  $i$  の 2 パターン目のテストパターンに対する出力応答を格納するレジスタを  $MUX_j$  の応答レジスタとする。

$MUX_j$  の入力  $i$  の 1 パターン目テストレジスタ、 $MUX_j$  の入力  $i$  の 2 パターン目テストレジスタ、 $MUX_j$  応答レジスタを合わせて  $MUX_j$  の入力  $i$  のテストレジスタとする。

図 1(b)において、あるハードウェア要素のテスト時に  $R0_0$  に 1 パターン目のテストパターン、 $R0_1$  に 2 パターン目テストレジスタが印加されているとする。このとき、 $R0_0, R0_1$  は M1 の入力 00 の入力レジスタであるので、 $R0_0$  は M1 の入力 00 の 1 パターン目テストレジスタとなる。 $R0_1$  は M1 の入力 00 の 2 パターン目テストレジスタとなる。

また、M1 の入力 00 の 2 パターン目のテストパターンに対する出力応答を格納するレジスタは  $R1_2$  である。このとき、 $R1_2$  は M1 の応答レジスタとなる。

## 2.2 テストレジスタの割当て

あるハードウェア要素のテスト時に  $MUX_j$  の入力  $i$  の 1(2) パターン目テストレジスタを決定する操作を  $MUX_j$  の入力  $i$  の 1(2) パターン目テストレジスタの割当てと定義する。同様に  $MUX_j$  の応答レジスタを決定する操作を  $MUX_j$  の応答レジスタの割当てと定義する。

$MUX_j$  の入力  $i$  の 1 パターン目テストレジスタの割当て、 $MUX_j$  の入力  $i$  の 2 パターン目テストレジスタの割当て、 $MUX_j$  の応答レジスタの割当てを合わせて  $MUX_j$  の入力  $i$  のテストレジスタの割当てと定義する。

## 2.3 MUX の入力のテスト

本論文では  $MUX_j$  の入力  $i$  について以下の条件をすべて満たすとき、 $MUX_j$  の入力  $i$  のテストが可能と定義する。

(i)  $MUX_j$  の入力  $i$  の 1 パターン目テストレジスタが割当てられている。

(ii)  $MUX_j$  の入力  $i$  の 2 パターン目テストレジスタが割当てられている。

(iii)  $MUX_j$  の応答レジスタが割当てられている。

$MUX_j$  の入力  $i$  のテスト時において、 $MUX_j$  の入力  $i$  の 1 パターン目テストレジスタと  $MUX_j$  の入力  $i$  の 2 パターン目テストレジスタの両方が割当てられるためには、1 時刻目と 2 時刻目の  $MUX_j$  の制御信号が同じである必要がある。

## 2.4 MUX の制御信号線のテスト

本論文では  $MUX_j$  の制御信号について以下のように定義する。

$$MUX_{j,sel} = \{x_n, x_{n-1}, \dots, x_1\} (x_{i^*} \in \{0, 1\})$$

$MUX_{j,sel}$  :  $MUX_j$  の制御信号の集合

$n$  : 制御信号幅

$i$  : 1 から  $n$  までの任意の整数

$x_i$  :  $MUX_j$  の制御信号線

本論文では以下の条件をすべて満たすとき  $MUX_j$  の制御信号線  $x_a$  の立上り遷移故障もしくは立下り遷移故障のテストが可能であるとする。

- (i) 1 時刻目の  $MUX_j$  の制御信号線  $x_a$  と 2 時刻目の  $MUX_j$  の制御信号線  $x_a$  のみ遷移している。

- (ii)  $MUX_j$  の制御信号線  $x_b$  ( $a \neq b$ ) の値が 1 時刻目と 2 時刻目で同じである。

- (iii) 1 時刻目の  $MUX_j$  の制御値  $p$  及び 2 時刻目の  $MUX_j$  の制御値  $q$  に対応する  $MUX_j$  の入力  $i_p, i_q$  に 2 パターン目のテストパターンが印加できる。

- (iv)  $MUX_j$  の応答テストレジスタが割当てられている。

1 時刻目の  $MUX_j$  の制御信号線  $x_a$  と 2 時刻目の  $MUX_j$  の制御信号線  $x_a$  を比較したとき、0 から 1 に遷移したとき立上り遷移故障のテストが可能、1 から 0 に遷移したとき立下り遷移故障のテストが可能とする。

このとき、2 時刻目の  $MUX_j$  の制御値は通常時では制御値  $q$  の制御に基づいて動作するが、故障時では制御値  $p$  の制御に基づいて動作する。そのため、 $MUX_j$  の制御信号線の故障伝搬の際には 2 時刻目の  $MUX_j$  の制御値  $p$  及び 2 時刻目の  $MUX_j$  の制御値  $q$  に対応する  $MUX_j$  の入力  $i_p, i_q$  の 2 パターン目テストレジスタの割当てをする必要がある。

## 2.5 レジスタの制御信号線のテスト

本論文では、以下の条件をすべて満たすときホールド機能付レジスタ  $j$  の制御信号線の遷移故障のテストが可能であるとする。

- (i) 1 時刻目のホールド機能付レジスタ  $j$  の制御信と 2 時刻目のホールド機能付レジスタ  $j$  の制御値が遷移している。

- (ii) 2 時刻目のホールド機能付レジスタ  $j$  のデータ入力に値が印加されている。

1 時刻目のホールド機能付レジスタ  $j$  の制御信号線と 2 時刻目のホールド機能付レジスタ  $j$  の制御信号線を比較したとき、0 から 1 に遷移したとき立上り遷移故障のテストが可能、1 から 0 に遷移したとき立下り遷移故障のテストが可能とする。

### 3. コントローラ拡大による MUX のテスト手法

#### 3.1 コントローラ拡大

コントローラ拡大とは、回路のテスタビリティを向上させるために状態や状態遷移をコントローラに追加することである。

RTL データパス内の MUX やレジスタをテストする際、おおむね有効状態遷移で設計されている制御信号に基づいて MUX やレジスタの動作を制御している。ゆえに、MUX やレジスタの制御により 2 時刻目のテストパターンの正当化や応答レジスタでの故障観測が不能な可能性がある。そのため、MUX やレジスタのテストを可能にするための制御をする状態遷移を設計するためにコントローラ拡大を行う必要がある。

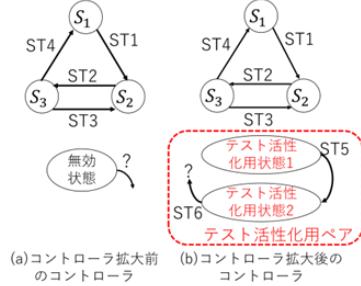

#### 3.2 テスト活性化用状態における状態遷移ペアの設計

本論文では、有効状態におけるハードウェア要素のテスト不能故障箇所をテストするための制御信号線の値を実現する状態遷移をテスト活性化用状態遷移と定義する。また、テスト活性化用状態遷移を実現するための状態をテスト活性化用状態とする。本論文では、テスト活性化用状態をコントローラの無効状態における状態遷移で設計する。

本論文では、ハードウェア要素のテスト不能故障箇所をテストするために、以下のテストレジスタの割当てを満たすような制御信号線の値を出力するテスト活性化用状態とする。

- (i) あるハードウェア要素のテスト不能故障箇所において、初期化するための 1 パターン目テストレジスタを割当てる制御信号。

- (ii) あるハードウェア要素のテスト不能故障箇所において、2 パターン目テストレジスタから故障励起経路を活性化するための制御信号。

- (iii) あるハードウェア要素のテスト不能故障箇所において、応答レジスタまで故障伝搬し観測するための制御信号。

本論文では、2 パターン目テストレジスタの正当化するための制御信号は考慮せずにテスト活性化用状態を設計するものとする。そのため、2 パターン目テストレジスタの正当化するための制御信号は論理合成によって依存する。

コントローラには、機能動作時には遷移しない無効状態が存在する場合がある。したがって、本手法ではコントローラに存在する無効状態を用いてコントローラ拡大を行うことで、テスト時にのみ動作する状態をテスト活性化用状態の状態遷移によって実現する。なお、コントローラ拡大時に無効状態数が不足する場合はコントローラの状態レジスタのビット幅を増加させて新たな無効状態を生成する。

提案手法ではブロードサイドテスト方式を採用しているため、2 時刻分のテスト活性化用状態遷移を設計する必要がある。このとき、2 時刻目の状態遷移先は未定義とする。

本論文では、2 時刻分のテスト活性化用状態遷移を設計するために 2 状態分のテスト活性化用状態を使用する。また、テストレジスタ割当てを実現するための 2 状態のテスト活性化用状態をテスト活性化用状態ペアとする。

図 2. テスト活性化用状態のコントローラ拡大

アと定義する。

図 2 にテスト活性化用状態のコントローラ拡大の例を示す。図 2(a)にコントローラ拡大する前のコントローラ、図 2(b)にコントローラ拡大によってテスト活性化用状態が 2 状態追加されたコントローラの例を示す。図 2(a)のコントローラは 2 ビットの状態レジスタで構成されているため 4 個の状態が存在する。

しかしながら、3 個の有効状態とそれらの間の状態遷移が設計されているため、1 個のテスト活性化用状態とその状態遷移しか定義することができない。そのため、図 2(b)においてコントローラの状態レジスタのビット幅を 1 つ増加させることで無効状態数を意図的に増やし、2 状態目のテスト活性化用状態においてその状態遷移を設計する。

状態遷移 ST5 では 1 パターン目テストレジスタから MUX 内の故障信号線の初期化をする制御信号を出力するように設計する。

同様に、状態遷移 ST6 では 2 パターン目テストレジスタから MUX 内の故障を励起・伝搬させ、応答レジスタで観測する制御信号を出力するように設計する。MUX のテストを実現するためのテスト活性化用状態の状態遷移が output する制御信号は、RTL データパス中の MUX、レジスタと、割当られたテストレジスタの情報を用いて、RTL データパスから容易に求めることができる。

#### 4. 実験結果

本論文ではフルスキャン設計が適用された ex2, ex4, sehwa, maha, kim の 5 つの RTL データパス回路の遷移故障を対象に実験を行った。実験ではテスト活性化用状態における状態遷移ペアの設計のみを行った。コントローラ拡大を適用しない通常のフルスキャン設計のみを適用した回路と、提案手法であるコントローラ拡大とフルスキャン設計を適用した回路に対して実験を行い、テスト不能故障数と故障検出率及び面積を評価した。RTL データパス信号線のビット幅は 16 ビットとした。論理合成及びフルスキャン設計ツールはそれぞれ Synopsys 社の Design Compiler と DFT Compiler を使用し自動テストパターン生成(ATO Test Pattern Generator: ATPG)ツールも同じく Synopsys 社の TetraMAX を使用した。また、対象故障モデルは遷移故障モデルとした。1 故障のテスト生成のバックトラック制限は 10,000 回に設定した。表 1 に RTL データパスの故障におけるテスト生成結果、表 2 にコントローラ拡大による回路全体の面積オーバーヘッド率の結果を示す。「Circuits」は実験対象の回路名を示し、「without」はコントローラ拡大を適用しない通常のフルスキャン設計回路に対する実験結果を示し、「proposed」は本手法を適用したフルスキャン

表1. テスト生成結果

| Circuit | without       |        |            |       |       |        |     | proposed       |               |        |            |       |       |        |     |                |

|---------|---------------|--------|------------|-------|-------|--------|-----|----------------|---------------|--------|------------|-------|-------|--------|-----|----------------|

|         | target faults | detect | untestable | abort | FC(%) | FE(%)  | #TP | ATPG Time(sec) | target faults | detect | untestable | abort | FC(%) | FE(%)  | #TP | ATPG Time(sec) |

| ex2     | 9906          | 9523   | 383        | 0     | 96.13 | 100.00 | 84  | 1.57           | 9906          | 9730   | 176        | 0     | 98.22 | 100.00 | 78  | 5.62           |

| ex4     | 8592          | 7810   | 782        | 0     | 90.90 | 100.00 | 85  | 6.99           | 8592          | 8286   | 304        | 2     | 96.44 | 99.98  | 83  | 15.14          |

| maha    | 7098          | 6445   | 650        | 3     | 90.80 | 99.96  | 117 | 4.32           | 7098          | 6784   | 312        | 2     | 95.58 | 99.97  | 106 | 1.66           |

| sehma   | 7976          | 7323   | 650        | 3     | 91.81 | 99.96  | 130 | 5.14           | 7976          | 7513   | 460        | 3     | 94.20 | 99.96  | 107 | 3.83           |

| kim     | 8128          | 7442   | 676        | 10    | 91.56 | 99.88  | 153 | 10.97          | 8128          | 7736   | 388        | 4     | 95.18 | 99.95  | 135 | 8.18           |

設計回路の実験結果を示す。表1において、「target faults」は対象故障数、「detect」は検出故障数、「untestable」はテスト不能故障数、「abort」は打切り故障数、「FC」は故障検出率、「FE」故障検出効率、「#TP」はテストパターン数、「ATPG time」はテスト生成時間を示す。また表2において、「Area」は回路全体の面積、「#state」は有効状態数、「#IS」は無効状態数、「#TAS」はテスト活性化用状態数、「#total\_state」は有効状態数とテスト活性化用状態数の総和、「#add\_FF」はコントローラ拡大時に無効状態数の不足によって追加したスキャンFF数、「AreaOverhead」はコントローラ拡大を行わない通常のスキャン設計回路と比較したときの面積オーバーヘッド率を示す。面積オーバーヘッド率は以下の式で求めるものとする。

$$\frac{Area_{proposed} - Area_{without}}{Area_{without}} \times 100$$

*Area<sub>proposed</sub>* : 提案手法を適用した回路全体の面積

*Area<sub>without</sub>* : フルスキャン設計のみ適用した回路全体の面積

5つの回路に対して、テスト不能故障数を平均300個削減、最大でex4において478個の削減することに成功した。また、故障検出率は平均3.68%、最大でex4において5.54%の向上に成功した。面積オーバーヘッド率は平均5.89%、最大でkimにおける8.28%の増加で抑えることができた。また、テストパターン数も平均9.67%削減することに成功した。

## 5. おわりに

本論文では、遷移故障に対するスキャンテストを対象としたデータパス部の遷移故障検出率増加ためのRTLでのDFT法を提案した。今後の課題として、整数計画法(ILP)を用いたハードウェア要素のテストのテストレジスタ割当ての定式化、テスト圧縮を考慮したハードウェア要素のテストにおけるDFT法、テスト活性化用状態を考慮したATPGの提案などが挙げられる。

## 参考文献

- [1] 藤原 秀雄，“ディジタルシステムの設計とテスト，”工学図書株式会社、2004。

- [2] Angela Krstic, and Kwang-Ting (Tim) Cheng, “Delay Fault Testing for VLSI Circuit, Kluwer Academic Publishers, Boston, 1998.

- [3] Y. Sato, S. Hamada, T. Maeda, A. Takatori, Y. Nozuyama and S. Kajihara, “Invisible Delay Quality - SDQM Model Lights Up What Could Not Be Seen,” Proc. ITC, p. Paper 47.1, 2005.

- [3] J. Savir and S. Patil, “On Broad-side Delay Test,” VLSI Test Symposium, pp. 284-290 Sept. 1994.

- [4] J.Savir, “Skewd·Load Transition Test: Part 1: Calculus”, Proceedings of IEEE International Test Conference PP705-713, October 1992.

[5] N.K.Jha, and S.Cupta, Testing of Digital Systems, Cambridge University Press, Cambridge, 2003.

[6] M. J. Geuzebroek, J. Th. van der Linden, and A. J. van de Goor, “Test Point Insertion for Compact Test Sets,” Test Conference 2000. Proceedings. International, pp.292-301, NJ, USA, Oct.2000.

[7] S. Remersaro, J. Rajska, T. Rinderknecht, Sudhakar M. Reddy, I. Pomeranz, “ATPG Heuristics Dependant Observation Point Insertion for Enhanced Compaction and Data Volume Reduction,” IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, pp.385-393, MA, USA, Oct.2008.

[8] M. Yoshimura, T. Hosokawa, and M. Ohta, “A Test Point Insertion Method to Reduce the Number of Test Patterns,” IEEE the 11th Asian Test Symposium, pp.298-304, Guam, USA, Nov. 2002.

[9] L. M. FLottes, B. Rouzeyre, L. Volpe, “A controller resynthesis based method for improving datapath testability,” IEEE International Symposium on Circuits and Systems, pp.347-350, Geneva, Switzerland, May.2000.

[10] T. Masuda, J. Nishimaki, T. Hosokawa, and H. Fujiwara, “A Test Generation Method for Datapaths Using Easily Testable Functional Time Expansion Models and Controller Augmentation,” IEEE the 24th Asian Test Symposium, pp.37-42, Mumbai, India, Nov.2015.

[11] T. Hosokawa, S. Takeda, H. Yamazaki, M. Yoshimura, “Controller Augmentation and Test Point Insertion at RTL for Concurrent Operational Unit Testing,” IEEE 23rd International Symposium on On-Line Testing and Robust System Design (IOLTS), pp.17-20, Thessaloniki, Greece, July, 2017.

[12] T. Hosokawa, S. Takeda, H. Yamazaki, M. Yoshimura, “A Test Register Assignment Method Based on Controller Augmentation to Reduce the Number of Test Patterns,” IEEE 24th International Symposium on On-Line Testing and Robust System Design (IOLTS), pp.228-231, Costa Brava, Spain,

表2. コントローラ拡大による面積オーバーヘッド率

| Circuit | without |        |     |      | proposed  |      |              |         |                  |

|---------|---------|--------|-----|------|-----------|------|--------------|---------|------------------|

|         | Area    | #state | #IS | Area | #TASPpair | #TAS | #total_state | #add_FF | Area Overhead(%) |

| ex2     | 3209    | 6      | 2   | 3410 | 8         | 16   | 22           | 2       | 6.26             |

| ex4     | 3189    | 5      | 3   | 3290 | 6         | 12   | 17           | 2       | 3.17             |

| maha    | 2541    | 24     | 8   | 2679 | 8         | 16   | 39           | 1       | 5.43             |

| sehma   | 3017    | 26     | 6   | 3208 | 11        | 22   | 47           | 1       | 6.33             |

| kim     | 2730    | 24     | 8   | 2956 | 10        | 20   | 43           | 1       | 8.28             |