## 中間電位を考慮したアンバイポーラ素子のブリッジ故障動作評価

日大生産工(学部) ○池田 涼風 日大生産工 新井 雅之

### 1. はじめに

近年 CMOS 集積回路の性能向上や低消費電力化などを実現するために、MOSFET の微細化に関する様々な研究が行われているが限界が近づいている. そこで新たな MOSFET の研究が進められている. その一つにアンバイポーラ素子がある[1]. アンバイポーラ素子は、中間電位が入力されるとハイインピーダンス状態となる特性を持つが[2]、中間電位を考慮した故障や耐故障設計に関する研究は知られていない.

本研究では、アンバイポーラ素子における中間電位を考慮したブリッジ故障動作評価を行う. LTspice を用いてアンバイポーラ素子の動作モデルを作成し、それを用いて XOR ゲートを作成した. 2 個の XOR ゲートの入力に抵抗性ブリッジ故障を仮定し、それに対して動作点解析を行い入力パターンや故障箇所の違いでどのように出力が変化するかシミュレーションによって解析した.

### 2. アンバイポーラ素子

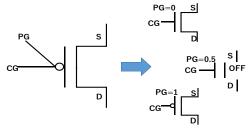

アンバイポーラ素子はゲート電極を従来の1個ではなく2個持ち、新たに用意したゲート電極(極性ゲート電極(PG))に加えられた電圧によってn型、p型を切り替えることができる[2]、PGに0V、1V、中間電位(0.5V)を加えた際の動作例を図1に示す、PG=0のときに10のののでは、10ののでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは、10のでは

図1 アンバイポーラ素子の動作例

# 3. アンバイポーラ素子を用いた論理 回路の故障モデルと評価

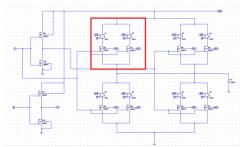

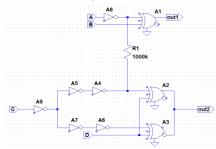

本研究ではアンバイポーラ素子の中間電 位による影響を考慮してシミュレーション を行った.しかし、シミュレーションに使用 したLTspiceにはアンバイポーラ素子が実装 されていない. そこでMOSFET(n型, p型)とス イッチを用いて近似モデルを作成し、それを 用いて2入力XORゲートのブリッジ故障につ いて考察した. シミュレーションで使用した XORゲートを図2に示す. 図2の太枠が1個の アンバイポーラ素子を表している. 2個のス イッチとnmos, pmosを1個ずつ用いてアンバ イポーラ素子の動作を表現している. スイッ チに加えられる電圧が0~0.3Vのときに nmos, 0.7~1.0Vのときにpmosとして動作し 0.4~0.6Vのときスイッチが切り離されオフ 状態となる.

図2 アンバイポーラ素子を用いた XOR ゲートの近似モデル

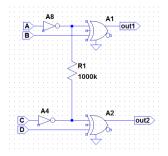

今回行ったシミュレーションは動作点解析である.動作点解析は抵抗値を $10\Omega$ から $1M\Omega$ まで10倍ずつ増やし出力電圧を測定した.動作点解析の入力はDC電圧で行い故障する箇所を変えシミュレーションを行った.図3、5は今回使用した故障モデルであり、図3、5においてA、Cはゲート電極(CG)B、Dは極性ゲート電極(PG)を表している.

Evaluation of Bridge Fault Behaviors on Ambipolar Devices Considering Intermediate Voltage

Ryoka IKEDA and Masayuki ARAI

図3 XORゲートのブリッジ故障

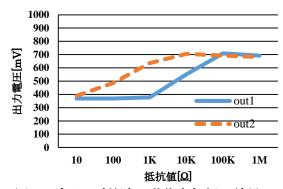

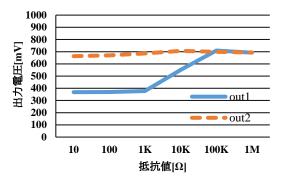

図3はXORゲートのブリッジ故障を表している.動作点解析の結果を図4に示す.入力はA=1, B=1, C=0, D=0である.出力は入力ゲートA-C間でブリッジ故障が発生したと仮定したときの結果であり,グラフの実線が出力out1,破線が出力out2を表している.図4より抵抗値の上昇に伴い出力電圧が上昇している.この結果から,抵抗値が小さいときは中間電位の影響を受けやすく,抵抗値が大きくなるにつれ影響を受けにくくなることが分かる.

図4 ブリッジ故障の動作点解析の結果

ブリッジ故障に対する耐故障設計の一検討として2個並列に配置されたXORゲートのうち一方のXORゲートを2重化した回路を作成した. 図5に2重化した回路を示す.

図5 耐故障設計を施したXORゲート

動作点解析の結果を図6に示す.シミュレーションは図4と同じ条件で行った.グラフの実線が出力out1,破線が出力out2を表して

いる.図6より、2重化したXORゲートの出力 はあまり変化していない.すなわちブリッジ 故障による中間電位の影響を2重化すること によりマスクできていることを示している.

図6 2重化した回路の動作点解析の結果

### 4. まとめ

今回アンバイポーラ素子を用いた回路のブリッジ故障とその耐故障設計を提案しシミュレーションを行った.動作点解析を行った結果,2 重化したことによりブリッジ故障をマスクし中間電位の影響を受けないことが分かった.今後は極性ゲート電極に中間電位が入力された際の動作について考察していく.

#### 参考文献

- [1] S. Bobba, M. De Marchi, Y. Leblebici, G. De Micheli, "Physical Synthesis onto a Sea-of-Tiles with Double-Gate Silicon Nanowire Transistors," Proceedings of the 49th Annual Design Automation Conference, pp. 42-47, 2012.

- [2] P.E. Gaillardon, L. Amaru, J. Zhang, G. De Micheli "Advanced System on a Chip Design Based on Controllable-Polarity FETs," Design, Automation and Test in Europe Conference and Exhibition, 2014.

- [3] 高橋暖, 新井雅之, "アンバイポーラ素子のSea-of-Tilesレイアウトにおける予備タイルを用いた耐故障設計,"電子情報通信学会ディペンダブルコンピューティング研究報告, DC2015-75, No.382, pp.11-16, 2015.