# 劣化による読込み誤りを考慮した MLCPCM の

# 高信頼化手法に関する検討

日大生産工(学部) ○末光 慎也 日大生産工 新井 雅之

#### 1. はじめに

マルチレベルセル相変化メモリ(Multi-Level Cell Phase Change Memory: MLC PCM)は、高速な読み書きが可能な不揮発性メモリの一つとして注目されている[1]. MLC PCMでは、ノイズや劣化によって引き起こされる抵抗変化によるビット誤りに対する報告がある[1-3]. 本研究では、ノイズによる書き込み時のばらつきや劣化による読み込み時のばらつきを考慮したビット誤り率の評価を行う.

#### 2. MLC PCM と誤りモデル

相変化メモリ(Phase Change Memory: PCM)は、アモルファス相となっている合金の量を熱により制御し、高抵抗状態(リセット状態)を遷移することにより値を記憶する. MLC PCM は、抵抗値の間に複数の段階を作り、一つのセルに複数ビットを記憶することを可能とした PCM である[1].

PCMでは、内部ノイズの影響により、書き込まれる抵抗値にばらつきが発生し、書き込んだ値とは異なる値として保存される現象が問題となっている[2]. 誤り訂正符号を用いた場合のビット誤り率の評価に関する報告がある[2]. さらに、閾値変更及びグレイコードを用いた高信頼化手法によってビット誤り率を削減する手法についても報告をさ

れている [3].

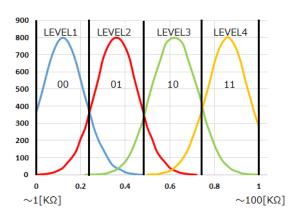

本稿では,ばらつきに対して正規分布を仮定する.図 1 に,2 ビット 4 レベルの MLC PCM における抵抗値のばらつき分布を示す.各レベルにおけるばらつきは,以下の関数の性質を満たすものとする. $\mu_X$ は, LEVEL X における平均値であり,各レベルの中間の抵抗値である. $\sigma_X$ は,標準偏差であり,すべてのレベルに対して一定である.

$$\mu_{X} = \begin{cases} \frac{1}{2.0*LEVEL} & (X = 0).\\ \mu_{X-1} + \frac{1}{LEVEL} & (other). \end{cases}$$

(1)

$$\sigma_{\chi} = \sigma. \tag{2}$$

図 1. 2 ビットの抵抗値のばらつき

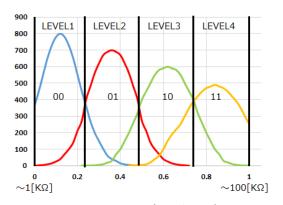

また,経年劣化による抵抗値の増大が原因で,読み込み時の抵抗値のばらつきがさらに増大するとの報告がある[2]. 図 2 に,2 ビット 4 レベルの MLC PCM における,劣化を考慮した抵抗値のばらつき分布を示す.劣化と

ともに標準偏差 $\sigma$ がレベルに対して線形増加する.

図 2. 2 ビットの劣化後のばらつき

### 3. 評価

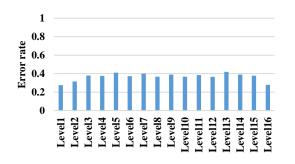

シミュレーションにより劣化による読み 込み誤りの評価を行う. 閾値が一定の 4 ビット 16 レベルの MLC PCM を対象とした. 各 レベルにおいて両側切断正規分布に従う乱 数を 10000 回生成し, 誤りをカウントする. 標準偏差 $\sigma$ として劣化を考慮した式(3)を適用 する.

$$\sigma_x = 0.03 + 0.002 * (x - 1).$$

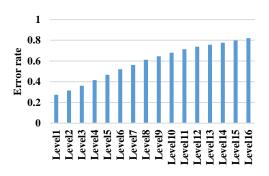

(3) 図 3, 及び図 4 に, 各 LEVEL を横軸として, 誤り率を縦軸にとったグラフを示す. 図 3 に, 書き込み時のばらつき考慮した 4 ビット 16 レベルの MLC PCM の誤り率を示す. 図 4 に, 経年劣化を考慮した 4 ビット 16 レベルの MLC PCM の誤り率を示す. まず図 3 では, 両端のレベルの誤り率が他のレベルと比べて低い.

図 3. 4 ビットの抵抗値のばらつき

また図4では、LEVELがあがるにつれて図3よりも大きく誤り率が上昇した。結果として、ばらつきと劣化を考慮したMLCPCMの誤り率の上昇を確認した。

図4. 4ビットの劣化後のばらつき

## 4. まとめと今後の課題

本稿では、ノイズによる書き込み時のばらつきや劣化による読込み時のばらつきを考慮したビット誤り率の評価を行った.抵抗値のばらつきは劣化後に大きく増加することが示された.今後は劣化による読込み誤りを考慮した誤り訂正符号の適用を考えている.

### 参考文献

- [1] B. C. Lee, E. Ipek, O. Mutlu et al., "Architecting Phase Change Memory As a Scalable DRAM Alternative," International Symposium on Computer Architecture, pp. 2– 13, 2009.

- [2] B. Li, S. C. Shan, Y. Hu, and X. Li, "Tolerating Noise in MLC PCM with Multi-Bit Correction Code," Pacific Rim International Symposium on Dependable Computing, pp. 226-231, 2013.

- [3]中野伸哉, 新井雅之"閾値変更に基づく MLC PCM の高信頼化手法に関する評価," 電子情報通信学会ディペンダブルコンピューティング研究会研究報告, No. 446, pp. 7-12, 2014 年.