# 自己組織化マップと必須割当て情報を用いた 同時検出可能故障の解析

日大生産工 〇武田 俊 日大生産工 山崎紘史 日大生産工 細川利典

日大生産工 新井雅之 日大生産工 山内ゆかり

#### 1. はじめに

近年,半導体微細化技術の進歩により,大規模 集積回路(Very Large Scale Integrated circuits: VLSI)が大規模化,複雑化している. さらに故障モデルの多様化に伴い, テストコスト の増加が問題となっている[1]. テストコストは テスタのテスト実行時間に比例して増加するた め、テストパターン数の削減などによるテスト実 行時間の削減が求められている. テストパターン 数の削減方法として、テスト圧縮[2]がある. テ スト圧縮を用いてテストパターン数を削減する ことにより、テストコストの削減が期待できる. テスト圧縮とは, 自動テストパターン生成 (Automatic Test Pattern Generator : ATPG) [3] により生成されたテスト集合のテスト品質を維 持したままテストパターン数を削減する技術で ある. テスト圧縮には、テスト生成の過程で圧縮 を行う動的圧縮[4][5]と、テスト生成後の初期テ スト集合に対して圧縮を行う静的圧縮[2][5]があ る. 静的圧縮の1つとして, MバイN法が提案 されている[6]. M バイ N 法は, テストパターン を N(N<M)個生成し,初期テスト集合に追加する ことで M 個のテストパターンを削除するテスト 圧縮法である.しかしながら、テスト生成には決 定的アルゴリズムを用いるため、1個のテストパ ターンで同時に検出可能な故障を効率よく分類 しないとテスト圧縮時の処理時間が大きくなる 可能性がある. それゆえ, ニューラルネットワー クの一種である自己組織化マップ(Self organizing maps: SOM) [7]を用いることで、複 数同時検出可能な故障を効率よく分類すること が期待できる.

本論文では、初期テスト集合に依存しないテスト圧縮法としてSOMと故障検出の必須割当て情報を用いた新たな手法を提案する。本論文の構成は以下のとおりである。第2章では従来のテスト圧縮手法としてMバイN法について述べる。第3章では,自己組織化マップについて述べ,第4章では必須割当てについて述べる。第5章では提案手法であるSOMと必須割当て情報を用いた同時検出可能故障の解析について述べる。第6章では実験結果を示し,第7章ではまとめと今後の課題について述べる。

## 2. MバイNアルゴリズム

M バイ N 法は、初期テスト集合 T から削除するテストパターンを M 個(M>N)選択し、選択したテストパターンを N 個生成する. 生成したテストパターンを N 個生成する. 生成したテスト集合と選択したテスト集合を置き換えることにより、テストパターン数を削減するアルゴリズムである. 以下に 3 バイ 2 法の例を用いて説明する. T からテストパターン t1, t2, t3 を選択した時、t1 でのみ検出可能な故障 f1, t2 でのみ検出可能な故障 f1, f2 を対象としたテスト生成を実行し、故障 f1, f2, f3 を検出可能なな ト生成を実行し、故障 f1, f2, f3 を検出可能な f3 としたとき、f1, f2, f3 を検出可能な f3 としたとき、f1, f2, f3 を検出可能な f3 としたとき、f1, f2, f3 を f3 としたとき、f1, f3 を f4 と f5 と f5 と f5 と f5 を f5 と f5 を f5 と f5 と f5 と f5 を f5 と f5 と f5 と f5 を f5 を f5 と f5 と f5 を f5 と f5 を f5 を f5 と f5 と f5 と f5 を f5 を f5 と f5 と f5 と f5 を f5 と f5 と f5 と f5 と f5 を f5 と f5 と

#### 3. 自己組織化マップ

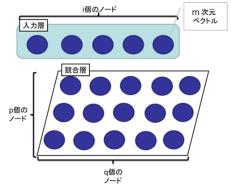

自己組織化マップ(SOM)とはニューラルネットワークの一種で、教師なし強化学習と近傍学習により、多次元ベクトルを二次元マップなどに写像する. これにより SOM に与えたデータが類似度の高いデータごとにマップ上に配置される. この性質より SOM は複雑なデータのクラスタリングに用いられる. SOM の入力層は i 個の m 次元のベクトルで表現され、競合層は  $p \times q$  個の任意の数の 2 次元配列で表現される. SOM の競合層の各ノードは、入力ベクトルと同じ次元(m 次元)の重みベクトルを用いて対応している. SOM の概略図を図 1 に示す.

図 1. SOM の概略図

An Analysis of Simultaneously Detectable Faults Using Self Organizing Maps and Necessary Assignment Informations

Shun TAKEDA, Hiroshi YAMAZAKI, Toshinori HOSOKAWA, Masayuki ARAI and Yukari YAMAUCHI

競合層のベクトルは、ランダムに初期化するか入力ベクトル集合の中央値に近いものを割当てる. SOM の学習は、入力ベクトルの特徴を繰り返し競合層に学習させることにより実行される. 提示された入力ベクトルに対して、最も類似度の高い競合層ノードを勝者ノードと定義し、勝者ノードとその周辺のノードに対して重みベクトルを更新することで学習を実行する. 重みベクトルの更新は、入力ベクトルに近づける方向に更新することで入力ベクトルの特徴を学習する. それにより、競合層には似た特徴を持ったノードが近くに集まる. 本論文では、この性質を利用してテスト圧縮を実現する.

#### 4. 必須割当て

必須割当てとは故障を検出するために一意に 決定される信号線の論理値である.

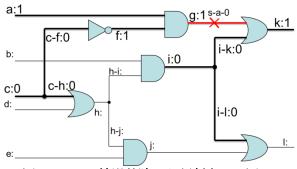

例を図2に示す.

図2. gの0縮退故障の必須割当ての図

図 2 において、太線の信号線に割当てられている 0 または 1 の値が信号線 g の 0 縮退故障の必須割当てである.

## 5. 自己組織化マップと必須割当て情報を用い たテスト圧縮

本章では、自己組織化マップと必須割当て情報を用いたテスト圧縮について説明をする.本手法は複数故障の同時故障検出テスト生成の対象とする故障を選択することを目標にSOMに必須割当て情報を与え、類似度の高い必須割当てを見つける.類似度の高い必須割当てを持つ故障を同時故障検出テスト生成の対象とすることによって、より効率的なテスト圧縮を目指す.

入力データのデータ長は対象回路の信号線数分存在し、4値で表現する.4値は必須割当ての0、必須割当ての1、必須割当てではないが、故障の励起または故障影響の伝搬、未正当化信号線の正当化に関係する可能性のある X1、必須割当てでなく、故障検出のための割当てが必要でないX2である.

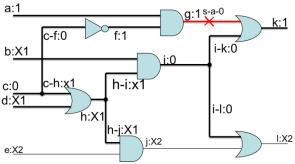

例を図3に示す.

図3. gの0縮退故障の値割当ての図

各信号線には図3に示すように必須割当て(0または、1)、X1、X2 のいずれか1 つの値が割当 てられる.図3 の回路図中の太線の信号線が故障 を励起および故障の影響の正当化に関係する可能性のある信号線であるためX1 が割当てられる。

SOM では勝者ノードを入力データと最も類似 度の高い競合層のノードとする. そのため, 入力 データと競合層のノードの各要素の差の 2 乗和 で類似度を求めるユークリッド距離を用いるが、 本論文では、SOM の入力層に与えるデータは必 須割当て情報であるため従来手法で用いられて いるユークリッド距離[8]が近い競合層のノード を勝者ノードとしない. 必須割当ては故障を検出 するために一意に割当てられる値である. したが って,必須割当ての値が衝突した場合に必須割当 ての類似度が低くなるためユークリッド距離は 採用しない. 本手法では必須割当ての 0 と 1 が 衝突した回数が最も少ないノードを勝者ノード とする. また, 0と1の衝突回数が同じだったノ ードが複数存在する場合, X1 と必須割当て(0 ま たは、1)または X1 と X1 の衝突と X2 の衝突を ペナルティ関数を用いて勝者ノードを選択する.

#### 5-1. SOM アルゴリズム

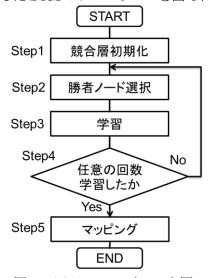

提案した SOM のアルゴリズムを図 4 に示す.

図 4. SOM フローチャート図

#### Step1

入力データは  $X=(x_1,x_2,...,x_n)$ である. n は入力データの要素数を表す. 入力データ $x_i$ は各信号線の情報 $l_{i1},l_{i2},...,l_{im}$ を全ての信号線数分保持し、m は信号線数を表す. 信号線 k の信号線情報を持つ $l_{ik}$ は 0, 1, X1, X2 の 4 状態に対応する 4 変数を持ち最も値が大きい変数を信号線 $l_{ik}$ の状態とする. 入力データ集合 X の入力データをランダムに選択し、その値をもとに競合層の値を初期化する.

#### Step2

入力データ集合 X からランダムに入力データ を 1 個選択し,入力ノード $x_i$ とする. $x_i$ と類似度 の高い競合層のノードを調べるために最初に競 合層の各ノードとの信号線の必須割当ての衝突 の回数を求める. 必須割当ての衝突の回数が最も 少なかった競合層のノードを第1候補とする.次 に入力データと第一候補の競合層の各ノードの 信号線情報の値の差を求める. ただし求める値は 競合層の信号線情報の 4 変数内で最も値が大き かった変数の値と入力ノード $x_i$ の対応する信号 線の変数の値の差のみである. 求めた差をもとに ペナルティ関数からペナルティ値を求める. ペナ ルティ関数は目標とする入力データと競合層ノ ードの差が大きいほどペナルティ値が急激に増 大する. また、様々回路規模の回路に対応できる ように対象回路の信号線数をペナルティ値の最 大とする.

図5にペナルティ関数の例を示す.

図 5. ペナルティ関数

次に差を求めた信号線で競合層と入力データで信号線の値に衝突が起きていないか判定をする. 必須割当ての 0, 1 の衝突が起きていた場合にはペナルティ値を大きく増大させ, X1 の衝突を起こしていた場合にはペナルティ値を減少させる. 必須割当ての 1, 0 の衝突が起きていない場合か X2 が存在する場合にはペナルティ値を大きく減少させる.

信号線ごとにペナルティ値を求めてその合計値が最も低い競合層のノードを勝者ノード  $\mathbf{c}$  とする.

#### Step3

勝者ノードとその周辺に $x_i$ の値の学習を行う.本論文では、(1)の学習式を用いて重みベクトルの更新を行った。(1)式において、t は現在の学習の繰り返し回数を表し、 $w_j(t)$ は現在(時刻 t)のノードの重みを表している。

$$w_{j}(t+1) = w_{j}(t) + h_{ci}(t)(x_{i} - w_{j}(t))$$

(1)

$h_{ci}(t)$  は学習の強度を表現する近傍関数であり、(2)式により求められる。(2)式において、 $r_c$ は勝者ノードcの競合層上での座標、 $r_j$ は競合層ノードjの座標をそれぞれ表している。 $|r_c-r_j|$ では差の絶対値を求めることで勝者ノード $r_c$ との距離を求めている。この差が小さいほどに学習係数 $h_{ci}(t)$ が小さくなり学習の影響が少なくなる。また、 $\alpha$ (t)と $\sigma$ (t) は学習を制御するパラメータであり、本論文では学習回数の増加につれ 1 から 0 までの値をとる単調減少関数を用いた。したがって、勝者ノードから近い参照ノードが強く学習する。

$$h_{ci}(t) = \alpha(t) \cdot \exp(\frac{|r_c - r_j|}{2\sigma^2(t)})$$

(2)

## Step4

指定された回数学習していない場合は Step2 へ.

### Step5

入力データ集合の入力データに対して競合層 内で最も類似度の高いノードを Step2 と同様の 方法で選択する. 選択された競合層ノードに入力 データを割当てる. この処理を全入力データに行 うことで競合層内のどの座標に入力データが存 在すかわかる. この処理をマッピングという.

#### 6. 実験結果

SOM の実験結果を図 6 に示す。ISCAS'89 ベンチマーク回路の s14207 の組合せ回路を対象とした。対象故障は Synopsys 社の TetraMAX と乱数を用いて生成した 10,000 個のテストパターンで故障シミュレーションを実行し,検出回数 100 回以下の故障とした。

対象故障数 3273 学習回数 50,000 回 競合層のサイズ 60 ×60 の 36,000

また、図 6 の同一の座標にマッピングされた故障同士に対して MTTG(Multi Target Test Generation)を行った. 対象とした故障はランダムに選択した 2 つ以上の故障がマッピングされている競合層のノードとした. 結果を表 1 に示す.

表 1. MTTG 結果

| 27 1. MILI O MAN |                                 |             |

|------------------|---------------------------------|-------------|

| ノード名             | 対象故障数                           | 成否          |

| node1            | 3                               | 0           |

| node2            | 2                               | 0<br>0<br>× |

| node3            | 48                              |             |

| node4            | 26                              | ×           |

| node5            | 75                              | ×           |

| node6            | 9                               | 0           |

| node7            | 2                               | 0           |

| node8            | 31                              | 0           |

| node9            | 3                               | 0           |

| node10           |                                 | ×           |

| node11           | 2                               | 0           |

| node12           | 2                               | 0           |

| node13           | 2                               | 0           |

| node14           | 2<br>2<br>2<br>2<br>2<br>2<br>3 | 0           |

| node15           | 3                               | ×           |

| node16           | 4                               | ×           |

| node17           | 4<br>2<br>2                     | ×           |

| node18           | 2                               | 0           |

| node19           | 4                               | 000         |

| node20           | 5                               | 0           |

| 成功数              |                                 | 12/20       |

半分以上のノードで MTTG が成功している. また、対象故障数が多いノードは MTTG が失敗 する傾向がみられる.

#### 6. おわりに

M バイ N 法による圧縮のための必須割当てを用いた SOM を提案した. 今後は MTTG がさらに成功するような SOM アルゴリズムを考えていきたい.

#### [参考文献]

- Y.Sato, T.Ikeda, M.Nakao, and T.Nagumo,: "Abist approach for very deepsub-micron (vdsm) defect, "Proc. International Test Conference, pp. 283291, 2000.

- K. Miyase, S. Kajihara and Sudhakar M. Reddy: "A Method of Static Test Compaction Based on Don't Care Identification," IPSJ Journal, Vol.43, No.5, pp.1290-1293,2002.

- 3) Tracy Larrabee: Test Pattern Generation Using Boolean Satisfiability, IEEE TRANSACTION ON COMPUTER-AIDEDDESIGN, VOL.11, No.1, pp4-15, 1992.

- 4) P.Goel and B.C.Rosales: "Test Generation and Dynamic Compaction of Tests", Digest of Papers 1979 Test Conf., pp.189-192, 1979.

- 5) S. Kajihara, I. Pomerantz, K. Kinoshita, and S. M. Reddy: "Cost-Effective Generation of Minimal Test Sets for Stuck-at Faults in Combinational Circuits," IEEE Transaction On Computer-Aided Design Of Integrated Circuits And System, Vol. 14, No. 12, pp 1496-1504, 1995.

- 6) Ilker Hamzaoglu and Janak H. Patel: "Test Set Compaction Algorithms for Combinational Circuits", Computer-Aided Design, 1998. ICCAD 98, pp.283 289, 12 Nov. 1998

- 7) T. Kohonen: "Self-Organizing Maps", Berlin, Springer, 2010.

- 8) Per-Erik Danielsson:" Euclidean Distance Mapping", Computer Graphics and Image Processing,pp.227-248,1980