## アンバイポーラ素子を用いた高信頼化回路設計及び

## 故障モデルの考察

日大生産工(学部) ○高橋 暖 日大生産工 新井 雅之

### 1 まえがき

CMOS集積回路の高速化,高集積化,低電力化への要求に伴い,立体構造やシリコンナノワイヤ,カーボンナノチューブなど新しいMOSFET構造の開発が進められている[1][3].またアンバイポーラ(双極性)素子にも注目が集まっている[2][3].しかしこれらの新しいMOSFETにおける冗長化モデルや耐故障性についてはあまり検討されていない.そこで本研究では,アンバイポーラ素子を用いた高信頼化回路設計と故障モデルについて評価を行った.

# 2 アンバイポーラ素子を用いた高信頼化回路 設計

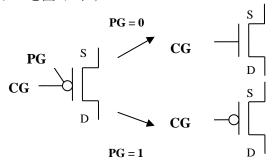

アンバイポーラ素子はMOSFETのゲート電極を従来の1個ではなく2個持ち,新たに用意したゲート電極(Polarity Gate: PG)で電圧を印加することによってn型,p型の動作を切り替えて使用することが可能である[2][3]. これはPGにより印加される電圧によってソース-ドレイン間のキャリアタイプが制御可能になるためである.アンバイポーラ素子の回路記号と動作モデルを図1に示す.

図1 アンバイポーラ素子の記号と動作モデル

PGを0にするとn型として動作し、PGを1にするとp型として動作し、また従来と同様の電極 (Control Gate: CG)によりトランジスタの ON/OFFが制御される。これにより回路設計の

際に使用されるトランジスタ数を減少させることが出来る.

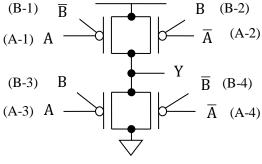

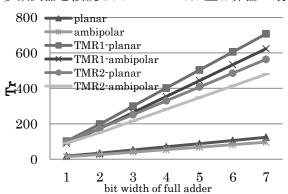

XORゲートは従来型において12個のトランジスタが必要であったが、アンバイポーラ素子を用いると図2に示すとおり8個のトランジスタで構成可能である[2][3]. そこでアンバイポーラ素子を用いた場合と用いなかった場合における、回路の2重系及びTMR高信頼設計での使用トランジスタ数を比較した. 全加算器のTMRにおけるトランジスタ数の比較を図3に示す.

図2 アンバイポーラXORゲート

図3における全加算器はXORゲートを用いた半加算器2個とORゲートから構成されている. TMR1では各桁の全加算器の出力それぞれに 多数決器を接続した. TMR2では全加算器の最

図3 全加算器におけるトランジスタ数の比較

Study on Dependable Design by using Ambipolar Device and Its Fault Model

Dan TAKAHASHI, Masayuki ARAI

終出力のみに多数決器を接続している. TMR1 ではトランジスタ数が従来型とアンバイポーラ型を比較して約12%削減された. TMR2では約15%の削減となった. 多数決器に使用されるトランジスタ数を考慮すれば差があると十分言える.

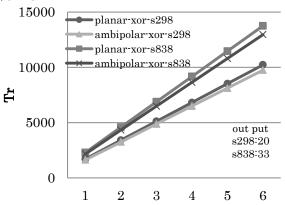

図4 s298,s838ベンチマーク回路2重化構造に おけるトランジスタ数の比較

次にs298, s838ベンチマーク回路の2重化構造におけるトランジスタ数の比較を図4に示す. s298では5%の削減となり, s838では6%の削減となった. 2重系ではXORゲートを回路の出力につなげるため,出力の多いs838の差がs298と比べ大きくなっている.

### 3 アンバイポーラ素子を用いた論理回路の 故障モデル

次に、XORゲートの故障モデルについて考察 した. 図2のXORゲートの4個のトランジスタは PGであるBの信号によってn型, p型が切り替わ る. そこでA、Bに接続される各ゲートが故障し た場合について出力される値(Y)をLTspiceで シミュレーションを行い調査した.表1,表2, 表3に、図2におけるゲート(A-1)~(A-4), (B-1)~(B-4)のうち一部が故障した際の出力の 値を示す. 通常のXORゲートでは出力(Y)と して(0,1,1,0)が出力される. 今回中間電位の出 力をH (0.61V以上0.9以下), M (0.4V~0.6V), L (0.39V以下0.1以上)と3通りに分けている. シミ ュレーションした多くの故障モデルにおいて, 中間電位が多く出力された.表3はゲート入力 Bの全故障によりn型,p型が全て逆になるため 出力が反転している.今後XORゲート以外の論 理ゲートに対して出力を調べる予定である.

### 4 まとめ

本稿ではアンバイポーラ素子を用いた高信頼化回路設計についてゲート数削減および有用性の面から評価を行った. XORゲート及び出

力が多い回路においては有用性があるといえる. 故障モデルにおいてはA,Bがそれぞれ故障した場合のシミュレーションを行い出力される値について評価を行った. シミュレーションでは中間電位の出力が多いため,その際の動作及び対策を検討していく必要がある.

#### 参考文献

- [1] 岩井洋, 角嶋邦之, "シリコンナノワイヤ FET技術," 電子情報通信学会誌, Vol95, No. 4, pp. 278-283, 2012年.

- [2] Pierre-Emmanuel Gaillardon, Luc Amaru, Jian Zhang, Giovanni De Micheli, "Advance System on a Chip Design Based on Controllable Polarity FETs," Design, Automation and Test in Europe Conference, paper 9.1.2, 2014.

- [3] M. Haykel Ben-Jamaa, Kartik Mohanram, Giovanni De Michel, "An Efficient Gate Library for Ambipolar CNTFET Logic," IEEE Transactions on Computer-Aided Dessign of Integrated Circuits and Systems, Vol. 30, No. 2, pp. 242-255, 2011.

表1 (A-1), (A-2)故障

| A | В | Y |

|---|---|---|

| 0 | 0 | M |

| 0 | 1 | M |

| 1 | 0 | 0 |

| 1 | 1 | M |

表2 (B-2), (B-3)故障

| A | В | Y |

|---|---|---|

| 0 | 0 | L |

| 0 | 1 | Н |

| 1 | 0 | L |

| 1 | 1 | M |

表3 (B-1), (B-2), (B-3), (B-4)故障

| A | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |