VLSI の製造バラつきと経年劣化を考慮したアダプティブフィールドテストにおける パス選択法

日大生産工(院) 〇柏崎 智史 日大生産工 細川 利典 九大 吉村 正義

## 1. はじめに

近年半導体製造技術の進歩に伴い、微小な遅延を引き起こす欠陥が増加している[1][2].これらの欠陥の中には、製造された超大規模集積回路(Very Large Scale -Integrated Circuits:VLSI)が出荷される際の出荷テストでは、欠陥として検出されないが、出荷後フィールド上の高温多湿など、過酷な環境でLSIが使用され続けた結果、経年劣化を起こし、欠陥として現れる場合が存在する。このような、フィールド上でのVLSIの欠陥の発生が重大な問題になっている[3].そのため、出荷後のフィールド上でテストを行うフィールドテストが提案されている[4][5].

一般に、経年劣化による微小遅延故障を検出するためには、パス遅延故障モデル[6]を対象に回路内のパスを網羅的にテストすることが理想的である。しかしながら、パス数は回路規模の指数乗に比例するため、テスト実行時間やコンピュータの処理能力の観点から網羅的にパスをテストするのは困難である。それゆえ、従来の微小遅延故障検出の方法として、擬似外部出力までの遅延時間が最も長いクリティカルパスを選択する方法と、パス全体の経年劣化による遅延時間の増分を予測し最長となるパスを選択する方法が存在する。

しかしながら、製造時に生じる不純物ばらつきや各トランジスタのじょう乱などにより製造されたすべての VLSI のそれぞれ対応するパスの遅延時間が同一にならないため、同一パスであってもパスの遅延時間は VLSI ごとに製造ばらつきが起きると考えられる.この製造ばらつきにより、設計時や経年劣化を考慮した結果選択されたパスより長いパスが現れる可能性がある.また、経年劣化により、遅延値が異なってくる可能性がある.したがって、実際にフィールドテストを行う際には、製造された VLSI ごとのランダムばらつきを考慮し、製造ばらつきの結果、最長パスとなる遅延時間が最も長いパスをテスト対象とするパス選択を行う方法が必要だと考えられる.

本論文では、各 VLSI に対するパス選択法を提案するための前段階として、製造ばらつきと経年劣化が発生した場合を仮定し、その結果設計時では、テスト対象パスではないパスが、テスト対象パスとしてどの程度選択されたかを解析した.

解析の結果,設計時ではテスト対象パスでないパスが,製造ばらつきによりテスト対象パスになってしまう可能性が存在することを確認した.

本論文では、まず第2章で経年劣化について説明する.第3章では、製造ばらつきについて説明する.第4章では、対象とする微小遅延故障について説明し、その検出例について説明する.第5章で、解析結果について述べる.

## 2. 経年劣化

VLSIの経年劣化の種類には、配線の遅延やトランジスタの劣化が考えられる[9]. 配線の遅延には、エレクトロマイグレーションやストレスマイグレーションがあげられる[10]. また、トランジスタの劣化の原因にはホットキャリア注入(Hot Carrier Injection:HCI)や負バイアス温度不安定性(Negative Bias Temperture Instability:NBTI)や、経時的絶縁破壊(Time Dependent Dielectric Breakdown:TDDB)などが存在する。本論文では、NBTIを対象にする.

#### 2. 1NBTI

NBTIとは、PMOSトランジスタの劣化現象の一つである [11]. PMOSトランジスタは、入力に負電圧が印加されると、ON状態になる.この状態が継続するとPMOSトランジスタの閾値電圧に変化が起こり、結果とし、トランジスタのスイッチング性能が低下する.

2. 2NBTI劣化モデル

本研究では、[11]で紹介されているNBTIの近似劣化モデルを使用する.

$$\Delta t = \mathbf{A} * \alpha^n * t^n * t_0 \tag{1}$$

ここで、 $\Delta$ tはNBTIによるゲート遅延増加量、Aは定数、 $\alpha$ は各PMOSトランジスタのオン状態の時間比率、tは回路の総使用時間、t0は非劣化時の遅延値である。nは 0.16程度でNBTIの特性を示す[11]. (1)式から、NBTIによる遅延増加量はPMOSトランジスタのオン状態の比率に大きく依存する.

# 3. 製造ばらつき.

近年VLSIの微細化に伴い,様々な種類の製造ばらつきが問題となってきている.製造ばらつきには,いくつか種類がある.その例を挙げると,電源電圧や環境温度により信号線の遷移時間などが変化するばらつき,ウエハー上に形成された信号線の遷移時間が各ウエハー間で異なるばらつき,同じウエハー内でチップのの所により信号線の遷移時間が異なるばらつきがある[9].他には,ウエハー上の個々のチップ内でのトランジスタ特性のばらつき.などの回路のレイアウトに依存し特性が変わってしまうばらつきがある[12].また,空間的な相関関係がなく信号線の遷移時間が異なるランダムばらつきが存在する.本論文では,ランダムばらつきを対象にする.

#### 3.1ランダムばらつき

本論文で取り扱うランダムばらつきとは、VLSI製造時に用いるシリコンウエハー上に形成したMOSトランジスタの閾値電圧などの特性が周りのトランジスタの影響に関係なくばらついてしまう現象のことを指す.

# 3.2ランダムばらつきの要因

ランダムばらつきは,空間的にまったく相関関係を持たないため,その原因として不純物ばらつきと,

# A path selection results of an adaptive field test with process variation and aging degradation for VLSI

Satoshi KASHIWAZAKI. Toshinori HOSOKAWA and Masavoshi YOSHIMURA

各トランジスタのじょう乱が原因として考えられている。VLSIの基盤に導入された不純物は離散的になっており、その数や位置の分布がトランジスタごとに異なり、その結果として生じる閾値電圧などのばらつきのことを不純物ばらつきという。各トランジスタのじょう乱は、製造されたトランジスタの形状がミクロレベルでみだれる現象のことである。

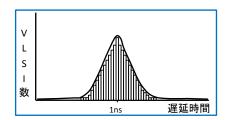

これら2つのランダムばらつきの原因のうち、影響が大きいとみられるのは、不純物ばらつきである. このようなランダムばらつきの結果製造された各 VLSIのあるトランジスタの遅延時刻は、次の図1のように正規分布するといわれている.

図1は設計時1nsの場合の正規分布とみなした場合の製造ばらつきの分布を表している.図1において縦軸はVLSI数,横軸は遅延時刻を表す.

図1. 製造ばらつきの分布例

## 4. 微小遅延故障モデル

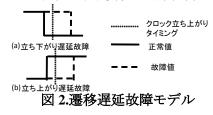

微小遅延故障とは、あるゲートや信号線において信号遷移が遅れる遷移遅延故障である。このモデルは、信号遅延の遅延影響が、ある特定のパスを伝搬したときのみ、FFに必ず伝搬する遅延時間の小さい故障モデルである。信号遷移とは、2パターンテストにおける第1時刻と第2時刻の論理値が0から1、または1から0へと変化する信号であり、それぞれ、立ち上がり遷移、立ち下り遷移と呼ぶ。

# 4.1遷移遅延故障モデル

遷移遅延故障モデルは、立ち上がり遅延故障と立ち下がり遅延故障の2つのモデルからなっている(図2).立ち下り遅延故障は、立ち下がり信号の第2時刻の論理値が0でなく1となる故障である図2(a).立ち上がり遷移故障は、立ち上がり信号の第2時刻の論理値が1でなく0となる故障である図2(b).

# 4.2 微小遅延故障検出パス選択方法

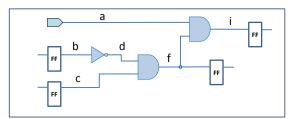

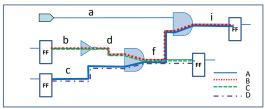

微小遅延故障を検出するためのパス選択方法とその問題点について図3の回路を用いて説明する.

図 3.微小遅延故障検出対象回路例

図3の回路は、クロック周期10ns、各信号線の遅延時刻を1ns、ゲートの立ち上がり遷移、立ち下り遷移遅延時間を各々AND 2ns、INV 1ns として設計されていると仮定する.

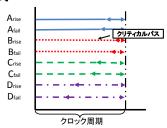

図3の回路から、回路内のFF間の全パス数が4本(図5のパスA,B,C,D)、である。各パスの立ち上がり遷移時間、立ち下り遷移時間を表1各パスの遅延分布を図4に示す。

表 4.各パス遅延時間

| パス名              | 遅延時間 |

|------------------|------|

| パスArize(c,f,i)   | 7ns  |

| パスAfall(c,f,i)   | 7ns  |

| パスBrize(b,d,f,i) | 9ns  |

| パスBfall(b,d,f,i) | 9ns  |

| パスCrize(b,d,f)   | 6ns  |

| パスCfall(b,d,f)   | 6ns  |

| パスDrize(c,f)     | 4ns  |

| パスDfall(c,f)     | 4ns  |

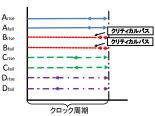

図 4.各パス遅延分布

図 4 において、縦軸はパス数、横軸は遅延時間を示している。クロック周期に対するマージンがいちばん小さいパス  $\mathbf{B}_{\mathit{rise}}$  と  $\mathbf{B}_{\mathit{fall}}$  がクリティカルパスである

図 5.FF 間の全パス

設計時の情報を元に微小遅延検出のためのテスト対象とするパス選択方法は、クロック周期に対するマージンが少ない順に(パス $B_{rize}$ パス $B_{fall}$ , パス $A_{rize}$ パス $A_{fall}$ , パス $C_{rize}$ パス $C_{fall}$ , パス $D_{rize}$ パス $D_{fall}$ ) となる。その理由は、パス $D_{rize}$  パス $D_{fall}$  がよるマージンが最も小さく、微小遅延故障を検出できる可能性が高く、パス $D_{fall}$  の順にマージンが大きくなるため、微小遅延故障が検出できる可能性が低くなると考えられるからである。次に各信号線に対して経年劣化を考慮した場合の遅延時間と各パス遅延分布例を表 2 と図 6 に示す。

表 5.各パス遅延時間

| パス名              | 遅延時間  |

|------------------|-------|

| パスArize(c,f,i)   | 7.4ns |

| パスAfall(c,f,i)   | 7.1ns |

| パスBrize(b,d,f,i) | 9.3ns |

| パスBfall(b,d,f,i) | 9.1ns |

| パスCrize(b,d,f)   | 6.4ns |

| パスCfall(b,d,f)   | 6.2ns |

| パスDrize(c,f)     | 4.5ns |

| パスDfall(c,f)     | 4.2ns |

図 6.経年劣化考慮時各パス遅延分布

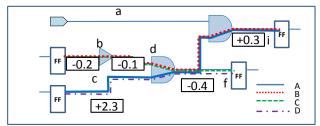

## 4.3 微小遅延故障検出パス選択方法の問題点

従来法での微小遅延故障検出法の問題点について 説明する. 図 7 に図 4 と同じであるが、各信号線で 製造ばらつきを考慮した場合の例を考える.

図 7.製造ばらつき考慮遅延時間

クロック周期を 10ns とする. 図 7 の各信号線上の 括弧内の値は、製造時に発生したランダムばらつき を考慮した遅延値を示している. 図 7 における各パ スの遅延分布図を表 3 と図 8 に示す.

表 1.各パス遅延時間

| パス名              | 遅延時間  |

|------------------|-------|

| パスArize(c,f,i)   | 9.3ns |

| パスAfall(c,f,i)   | 9.2ns |

| パスBrize(b,d,f,i) | 9.0ns |

| パスBfall(b,d,f,i) | 8.8ns |

| パスCrize(b,d,f)   | 5.7ns |

| パスCfall(b,d,f)   | 5.5ns |

| パスDrize(c,f)     | 6.4ns |

| パスDfall(c,f)     | 6.1ns |

図 8.製造ばらつき考慮時遅延パス分布

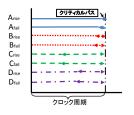

図 8 より,クリティカルパスが従来法で選択されたパス  $B_{rise}$ でなくパス  $A_{rise}$ になることがわかる.図 7 の回路に対して同様に各信号線に経年劣化による微小遅延故障があると仮定したとき,各パスの遅延時間分布を表 4 と図 9 に示す.

表 2.各パス遅延時間

| _ |                  | - 411.4 |

|---|------------------|---------|

|   | パス名              | 遅延時間    |

|   | パスArize(c,f,i)   | 10.2ns  |

|   | パスAfall(c,f,i)   | 10.1ns  |

|   | パスBrize(b,d,f,i) | 9.8ns   |

|   | パスBfall(b,d,f,i) | 9.6ns   |

|   | パスCrize(b,d,f)   | 6.2ns   |

|   | パスCfall(b,d,f)   | 6.0ns   |

|   | パスDrize(c,f)     | 7.0ns   |

|   | パスDfall(c,f)     | 6.4ns   |

|   |                  |         |

# 図9.製造ばらつき考慮時微小遅延故障遅延故障 の各パスの遅延時間

以上の例により、同じ回路であるが、製造ばらつきや経年劣化の結果テスト対象パスが変わる場合があることがわかる。このことから、従来法の問題点として、製造ばらつきや経年劣化を考慮しないでパス選択を行なった際、テスト対象としなければならないパスが、選択されず故障を検出できない可能性がある。

## 5. 解析結果

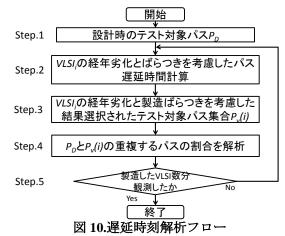

本論文では、製造された多数のVLSIの一つ一つに経年劣化と製造ばらつきを考慮し、フィールドテストに使用するパスを選択することにより、設計時にテスト対象パスを選択した場合と比べどの程度テスト対象パスが変化したかを解析した.

テスト対象パスの選択基準として、遅延時間が長い上位 X%のパス集合をテスト対象のパスとした.

また VLSI は、1000 個製造したものと仮定し、X、Y の値は固定とし、X=5、Y=1 とし、クロック周期は、最長パスの遅延時間に 5%のマージンを付け加えた値とした。また、経年劣化に必要な係数 A は、PMOSが常に ON の状態で 10 年間動かした際に最大 20%遅

延するように調整し、 $\alpha$ を求めるために 10,000 パターンランダムパターンシミュレーションを行った. 製造ばらつきは、正規分布で与え、平均は設計時の値分散は 0.05 とした. 解析フローを図 10 に示す.

Step1) 設計時にテスト対象パスとなるパス集合  $P_D$ を求める

Step2) 製造した VLSI ごとに経年劣化と製造ばら つきを考慮した遅延時間を求める

Step3) Step2 で求められた遅延時間より解析している  $VLSI_i$ でのテスト対象パス  $P_v(i)$ を求める

Step4)  $P_D$ と  $P_v(i)$ の重複する割合を求める.

Step5) 製造した VLSI 個数分解析を行う.

今回の解析において、パスの遅延時間はゲート段数に依存すると考えられる。そこで、本論文では、解析対象回路のゲート段数が等しくなるように回路に対して論理合成を行った。表 5,6 に論理合成前と論理合成後の遅延時間の最大値、最小値、平均遅延時間、分散、パス数を示す。

表 6. 論理合成前回路データ

| 回路名    | 最大値   | 最小値  | 平均    | 分散    | パス数     |

|--------|-------|------|-------|-------|---------|

| s9234  | 23.00 | 0.80 | 15.78 | 14.28 | 227837  |

| s13207 | 27.40 | 0.10 | 20.26 | 7.43  | 1005680 |

| s35932 | 11.00 | 0.70 | 9.15  | 2.63  | 122997  |

| s38417 | 22.07 | 0.10 | 13.94 | 9.69  | 1389348 |

| s38584 | 37.10 | 0.10 | 29.63 | 7.30  | 8550442 |

| b9     | 5.80  | 0.90 | 4.66  | 1.50  | 1183    |

| b11    | 17.50 | 0.90 | 8.91  | 7.77  | 10558   |

| b12    | 11.60 | 0.50 | 6.35  | 3.35  | 9607    |

表 7.論理合成後回路データ

| 回路名    | 最大値  | 最小値  | 平均   | 分散   | パス数    |

|--------|------|------|------|------|--------|

| s9234  | 6.45 | 0.10 | 4.75 | 1.10 | 13427  |

| s13207 | 9.30 | 0.10 | 6.65 | 4.08 | 29758  |

| s35932 | 4.75 | 0.45 | 2.92 | 1.06 | 14101  |

| s38417 | 9.75 | 0.10 | 6.89 | 1.44 | 563658 |

| s38584 | 9.85 | 0.10 | 6.92 | 4.07 | 37398  |

| b9     | 4.40 | 0.90 | 3.49 | 0.73 | 877    |

| b11    | 6.90 | 0.75 | 4.95 | 0.70 | 5366   |

| b12    | 6.80 | 0.55 | 4.77 | 1.03 | 10053  |

表 7 に,解析に用いた ISCAS'89, ITC'99 回路の回路情報と,クロック周期を示す.

表 8.回路情報

|     |     |     |     |      |        | クリティカル |            |

|-----|-----|-----|-----|------|--------|--------|------------|

| 回路  | 名   | PI数 | PO数 | FF数  | 全パス数   | パス(ns) | クロック周期(ns) |

| sg  | 234 | 12  | 22  | 160  | 13427  | 6.45   | 6.77       |

| s13 | 207 | 32  | 121 | 647  | 29758  | 9.30   | 9.77       |

| s35 | 932 | 35  | 320 | 1728 | 14101  | 4.75   | 4.99       |

| s38 | 417 | 28  | 106 | 1564 | 563658 | 9.75   | 10.24      |

| s38 | 584 | 13  | 278 | 1300 | 117356 | 9.85   | 10.34      |

|     | b9  | 1   | 1   | 28   | 877    | 4.40   | 4.62       |

|     | b11 | 7   | 6   | 31   | 5366   | 6.90   | 7.25       |

|     | b12 | 5   | 6   | 121  | 10053  | 6.80   | 7.14       |

表7の「回路名」は対象回路の名前,「外部入力数」

は回路の外部入力数,「FF 数」は回路内に存在するFF の数,「全パス数」は疑似外部入力(ppi)から疑似外部出力(ppo)の間のパス数,「クリティカルパス数」は回路内のクリティカルパスの遅延時間の値,「クロック周期」は,クリティカルパスの5%の値をマージンとして付加した後の時間を表す.

表 8, 9 に設計時に選択したパスが製造ばらつきの結果どのようにばらつきその重複する割合  $|P_D \cap P_v(i)|$  にどのように分布するかを示す.

表 8/基準2のパス重複率(設計時 VS 製造ばらつき)

|        | PpとP√(i)の重複率(%) |      |       |       |       |       |     |  |  |  |  |

|--------|-----------------|------|-------|-------|-------|-------|-----|--|--|--|--|

| 回路名    | 0               | 1~19 | 20~39 | 40~59 | 60~79 | 80~99 | 100 |  |  |  |  |

| s9234  | 0               | 3    | 0     | 2     | 2     | 993   | 0   |  |  |  |  |

| s13207 | 0               | 20   | 13    | 13    | 33    | 921   | 0   |  |  |  |  |

| s35932 | 0               | 8    | 85    | 126   | 120   | 661   | 0   |  |  |  |  |

| s38417 | 0               | 42   | 81    | 130   | 139   | 608   | 0   |  |  |  |  |

| s38584 | 0               | 56   | 109   | 71    | 93    | 671   | 0   |  |  |  |  |

| b9     | 4               | 6    | 4     | 7     | 904   | 75    | 0   |  |  |  |  |

| b11    | 0               | 7    | 8     | 12    | 15    | 958   | 0   |  |  |  |  |

| b12    | 0               | 23   | 30    | 7     | 5     | 935   | 0   |  |  |  |  |

表 8 の「回路名」は回路名を表し、重複率は、設計時にテスト対象パスとして選択された  $P_D$  に製造バラつきの結果テスト対象パスとなった  $P_V(i)$ がどれだけ含まれており、実際に複数個作成した際にどこに分布するかを示している.

表 9 に経年劣化を考慮してテスト対象パスを選択した場合と、経年劣化と製造ばらつきを考慮しテスト対象パスを選択した場合の重複率を表す.

表 9.基準2のパス重複率(劣化 VS 劣化とばらつき)

|         | P <sub>D</sub> とP <sub>v</sub> (i)の重複率(%) |      |       |       |       |       |     |  |  |

|---------|-------------------------------------------|------|-------|-------|-------|-------|-----|--|--|

| 回路名     | 0                                         | 1~19 | 20~39 | 40~59 | 60~79 | 80~99 | 100 |  |  |

| s9234'  | 0                                         | 456  | 544   | 0     | 0     | 0     | 0   |  |  |

| s13207' | 0                                         | 570  | 430   | 0     | 0     | 0     | 0   |  |  |

| s35932' | 0                                         | 113  | 887   | 0     | 0     | 0     | 0   |  |  |

| s38417  | 0                                         | 0    | 1000  | 0     | 0     | 0     | 0   |  |  |

| s38584' | 0                                         | 0    | 928   | 72    | 0     | 0     | 0   |  |  |

| p9.     | 810                                       | 39   | 47    | 46    | 58    | 0     | 0   |  |  |

| b11'    | 0                                         | 463  | 537   | 0     | 0     | 0     | 0   |  |  |

| b12'    | 0                                         | 608  | 392   | 0     | 0     | 0     | 0   |  |  |

表9の「回路名」の回路名の後ろについている(rise) と(fall)は、入力に立ち上がり遷移、立ち下り遷移が来た場合を示している。また、表9で値がすべて0になっている場所は、クロック周期に対する基準を満たすパスが存在しない場合である。

表 10, に設計時のテスト対象パスを選択した場合 と,経年劣化と製造ばらつきを考慮しテスト対象パ スを選択した場合の重複率を表す.

表 103. 基準2のパス重複率(設計時VS劣化とばらつき)

|         | PoとPv(i)の重複率(%) |      |       |       |       |       |     |  |  |

|---------|-----------------|------|-------|-------|-------|-------|-----|--|--|

| 回路名     | 0               | 1~19 | 20~39 | 40~59 | 60~79 | 80~99 | 100 |  |  |

| s9234'  | 0               | 456  | 544   | 0     | 0     | 0     | 0   |  |  |

| s13207' | 0               | 570  | 430   | 0     | 0     | 0     | 0   |  |  |

| s35932' | 0               | 113  | 887   | 0     | 0     | 0     | 0   |  |  |

| s38417' | 0               | 0    | 1000  | 0     | 0     | 0     | 0   |  |  |

| s38584' | 0               | 0    | 928   | 72    | 0     | 0     | 0   |  |  |

| b9'     | 810             | 39   | 47    | 46    | 58    | 0     | 0   |  |  |

| b11'    | 0               | 463  | 537   | 0     | 0     | 0     | 0   |  |  |

| b12'    | 0               | 608  | 392   | 0     | 0     | 0     | 0   |  |  |

表 8~10 より, 設計時にはテスト対象でないが経 年劣化や製造バラつきによりテスト対象となるパス が存在することが分かった.

## 6.結論

本論文では、製造ばらつきが回路ごとに発生した場合を仮定し、その結果設計時や経年劣化を考慮した際のテスト対象パスではないパスが、テスト対象パスとしてどの程度選択されたかを解析した.

解析結果より、設計時や経年劣化を考慮した結果 テスト対象パスにならないが、製造ばらつきを考慮 した結果テスト対象パスになる可能性があるパスが 多くあることが確認された.

## 文献

1) S Mitra , E Volkerink , E.J McCluskey ,SE ichender ,"Delay degect screening using process monitor structures,"Proceedings of 22<sup>nd</sup> IEEEV LSI Test Symposium 2004. pp 43-48,Sacrament o,April 2004

2)G Aldrich, B Cory, "Improving Test Quality and Reducing Escapes,"Proc. Fabless Forum, Fabless Semiconductor Assoc,pp 34-35,2003

3)M.Yilmaz, K.Chakrabarty,M.Teranipoor,"Test-p attern grading and pattern selection for small-d elay defects,"Proceedings of 26th IEEEVLSI Test Symposium,pp.233-239,Los Alamitos, April 2 008

4)P.H.Bardel, W.H.McAnney, and J.Savir, :Buil t-in test for VLSI, John Wiley and Sons, New York, 1987

5)T.Hiraide, K.O. Boateng, H. Konishi, K.Itaya, M. Emori, H.Yamanaka, and T. Mochiyama, "BIST-aided scan test-A new method for test cost reduction," Proceedings of 21st IEEE VLSI Test Symposium, pp.359-364,April 2003.

6)G.L.Smith,"Model for delay faults upon path s,"Proceeding of the International Test Conference,pp.342-349,1985.

7)Y.Sato, S.Hamada, T.Maeda, A.Takatori, S.Kaj ihara,"Evaluation if the statistical delay quality model," Asian and South Pacific Design Auto mation Conference,pp.305-310,2005

8)M.Noda, S.Kajihara, Y.Miura, Y.Sato, K.Miyas e, X.Wen, "On Estimation of NBTI-Induced Del ay Degradation," Test Symposium ETS 2010 15 th IEEE, pp.107-111, European, May 2010

9)M.Pelgrom, A.Duinmaijer, A.Welbers,"Matchin g properties of MOS transistors."IEEE Journal of Solid state Circuit,Vol.24,No.5,pp 1433-1439, Oct 1989

10) 林将志, 中野真治, 和田哲明, "Cu 配線のエレクトロマイグレーション現象", REAJ 誌, vol.25, no.2,pp.110-120, 2003.

11) S. Bhardwaj, *et al.*, "Predictive Modeling of the NBTI Effect for Reliable Design," *CICC*, 2 006.

11)K.okada, H.Onodera, K.tamaru,"Layout deoe ndent matching analysis of CMOS circuit."IEIC E Transactions on Fundamentals of Electronics, Cpmmunications and Computer Sciences, Vol. E8 2-A,No2,pp348-355,Feb 1999

12)J.A.Waicukauski, E.Lindbloom, B.L.Rosen, and V.S.Iyengar, "Transition fault simulation," Design & Test of Computers, IEEE, Vol.4, pp.32-38,