7-15

# 制御ポイントを用いた遷移故障検出用テストパターン数削減度の評価

日大生産工(院) 〇湯本 仁高 日大生産工 細川 利典 九大 吉村 正義

#### 1 はじめに

近年、半導体集積技術の進展に伴い、大規模集積回路(LSI:Large Scale Integration Circuit)が大規模化、高機能化している。したがって、テスト設計の工数が増大しており、その自動化技術が重要になっている。順序回路の自動テストパターン生成(ATPG:Auto Test Pattern Generation)は困難な問題であり、高い故障検出効率を得るテストパターンを生成するためには、フルスキャン設計[1][2]に代表されるテスト容易化設計(DFT:Design For Testability)が必要である。

LSI が大規模化、高集積化することにより、回路内のゲート数が増加しており、それに比例してテストパターン数も増加している[3]. また、縮退故障モデルのみでは検出することが困難なタイミング遅延を伴う欠陥や信号線間の短絡による欠陥も増加しており、縮退故障の検出に加えて遷移故障[4]や、ブリッジ故障[5]の検出が重要となっている.

テストパターン数増加の問題を解決するための一手法として、テストポイント挿入によりテスト圧縮率を高める手法が提案されている[6][7][8][9][10][11]. 回路内部の信号線にテストポイントが挿入された場合、その信号線は可制御かつ可観測となり疑似外部入出力として扱うことが可能になる. 回路内にテストポイント挿入することにより、外部入力とテスト集合中のドントケア数(X:don't care)が増加し、テスト圧縮の効率が高くなると考えられる. その結果テストパターン数が削減できると考えられている.

文献[6][7][8][9][10][11]のテストポイント挿入箇所探索アルゴリズムは、縮退故障に対してテスト圧縮の原理と、回路構造のみに着目し、回路構造上テスト圧縮困難であると予測される箇所にテストポイント挿入を行いテストパターン数の削減を図っている。また遷移故障に対するテストポイント挿入箇所探索アルゴリズムが提案されている[9][12][13].

文献[12]では、2パターン目をシフト動作で印加するスキュードロード方式[14][15]においてテストポイント挿入を行う手法が提案されている。文献[9][13]では、2パターン目を1パターン目の回路応答から印加するブロードサイド方式[16]においてテストポイント挿入を行う手法が提案されている。文献[13]では、遷移故障検出が容易になる箇所を探索し、テストポイント挿入を行っている。

遷移故障のテストは、信号線における値の遷移の遅延を検出するために、変化前の信号線値を設定するテストパターンと変化後の信号線値を確かめるテストパターンの2つのテストパターンを連続して印加し、故障の影響を観測するフリップフロップ(FF:Flip-Flop)

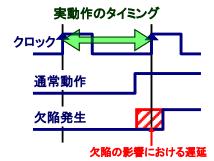

図 1. 立ち上がり遷移故障(R 故障)

まで伝搬する必要がある.したがって、内部の信号線に観測ポイントを挿入することは不可能である.よって本論文では制御ポイントを用いる.

本論文では、文献[13]で用いられている制御ポイントの構造を利用し、テスト圧縮の観点から遷移故障のテストパターン数を削減するような箇所に制御ポイントを挿入するアルゴリズムを提案する.

#### 2 遷移故障におけるテスト方法

遷移故障とは、論理ゲートの1つの信号線に遅延が発生する故障である。0から1に遷移する立ち上がり遷移故障(R 故障:slow-to-rise fault)と1から0に遷移する立ち下がり遷移故障(F 故障:slow-to-fall fault)の2 通り存在する。図1に立ち上がり遷移故障(R 故障)の例を示す。上からクロックの周期、通常動作での値を取り込むタイミング、欠陥が発生した場合での値を取り込むタイミングの波形を表している。また、矢印間は実動作でのタイミングを表し、斜線部分は欠陥の影響における遅延を表している。通常動作では1が取り込まれるのに対して欠陥が発生すると欠陥の影響により遅延が発生し0が取り込まれてしまう。このような故障 R 故障と呼び、F 故障ではこの事象と逆の事象が発生する.

Evaluation of a Control Point Insertion Method to Reduce the Number of Test Patterns for Transition Faults

Yoshitaka YUMOTO, Toshinori HOSOKAWA and Masayoshi YOSHIMURA

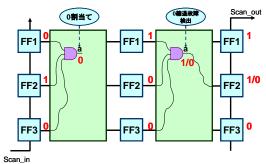

図3. ブロードサイド方式

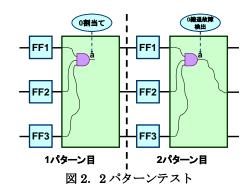

遷移故障を検出するためには、2つのテストパターンが必要となる。図 2に 2パターンテストにおいて R 故障の検出方法の例を示す。信号線 a の R 故障を検出するためには、1パターン目において信号線 a の値を 0 に設定するテストパターンを印加する。続けて 2パターン目において信号線 a で値の遷移が起こるように 1 に設定し、なおかつ出力で信号線 a の値の遷移が観測できるようなテストパターンを印加しなければならない。

遷移故障検出法である 2 パターンテストを用いた実 速度スキャンテスト法としてブロードサイド方式[16] がある. ブロードサイド方式では、フルスキャン設計 された回路に対してテストされる. 1 パターン目にお いてシフト動作によりテストパターンが印加される. 2 パターン目では、1 パターン目のテストパターンの 回路応答がテストパターンとなる.図3にスキャンFF が 3 つ(FF1, FF2, FF3)からなる順序回路において信 号線 a に R 故障が発生していると仮定する. まず始め に信号線 a に 0 を割当て可能なテストパターンを 1 パ ターン目に印加する. 例では, (FF1, FF2, FF3)=(0, 1,0)とテストパターンを印加する.次に1パターン目 の回路応答を FF に取り込むことにより 2 パターン目 のテストパターンとなり,各FFは(FF1,FF2,FF3)=(1, 0,0)となる.これより信号線 a での値の遷移が起こり, なおかつ FF2 により値の遷移を観測することが可能 になった.

# 3 テストポイント挿入技術3.1 テストポイント

テストポイントとは、テスト対象回路の内部信号線に論理回路を付加することである。主にテスト対象回路の可検査性の向上を図るという目的で用いられる。テストポイントが挿入された内部信号線は、外部入力またはスキャン FF で直接値を設定することが可能であり、なおかつ外部出力またはスキャン FF で直接値観測可能になる。このことから、テストポイント挿入するということは、内部信号線値を可制御・可観測[17]にするとして回路の内部信号線を疑似的に外部入出力として扱うことを可能にする。

テストポイントには制御ポイント,観測ポイント,制御・観測の両方の機能をあわせ持つテストポイントの3種類からなる.制御ポイントとは,内部信号線の可制御費[17]を向上させるためにテスト対象回路に疑似的に外部入力を付加することである.信号線 Cの1(0)可制御費というのは信号線 Cに信号線値1(0)を設定する難易度を示している.観測ポイントとは,内部信号線の可観測費[17]を向上させるためにテスト対象回路

図 5. 制御ポイントを挿入する利点

に疑似的に外部出力が付加されることである. 信号線 Cの観測費というのは,信号線 Cの信号線値を外部出力まで伝搬させる難易度を示している. テストポイントとは,制御・観測の両方の機能をあわせ持つ疑似外部入出力のことである.

本論文では、遷移故障を検出するテストパターン数の削減を目的としており、故障の影響を FF まで伝搬しなければならない. したがって、観測ポイントやテストポイントを挿入することは不可能である. よって本論文では制御ポイントを挿入する.

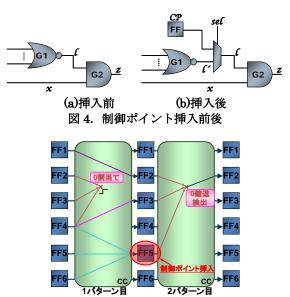

図 4 に制御ポイント挿入前後の回路例を示す.図 4(a)は制御ポイント挿入前の回路を示し、図 4(b)は制御ポイント挿入後の回路を示している.図 4(a)において信号線 x に故障の影響が伝搬していると仮定する.故障の影響を外部出力 z に伝搬させるためには、信号線  $\ell$  に 1 を設定する必要がある.しかし、G1 ゲートは他入力の NOR ゲートであり信号線  $\ell$  に 1 を設定するのは困難であるため、信号線  $\ell$  に制御ポイントを挿入する.制御ポイントは、マルチプレクサとスキャン FFを元の回路に付加することで実現できる.制御ポイントを挿入することによりスキャン FF に 1 を設定し、マルチプレクサの  $se\ell$  を 0 に制御することにより信号線  $\ell$ の値を 1 に制御することが可能となった.したがって、信号線 x の故障影響を外部出力 z で観測することが容易となる.

#### 3.2 制御ポイント挿入する利点

制御ポイントをブロードサイド方式に挿入する利点としてテストパターン中のX数が増加しテストパターン圧縮の効率が高くなることが挙げられる。図 5 に制御ポイントを挿入する利点の例を示す。ある信号線のR 故障を検出するためには、1 パターン目で0 を割当て、2 パターン目で0 縮退故障を検出するようなテストパターン印加する必要がある。このとき、0 縮退故障を検出するために値の影響を与えたスキャンFF (FF2, FF3, FF5)は1 パターン目から値の影響を受けている。図 5 の例では、FF2 はFF1, FF3 はFF4, FF5 はFF4, FF5, FF6 から値の影響を受けていると仮定する。このとき、1 パターン目のスキャンFF か

ら値の影響を多く受けているスキャン FF に制御ポイントを挿入する(図 5 の例では FF5)ことにより、スキャン FF の値の影響を緩和し、値の影響を及ぼしていた 1 パターン目のテストパターンのケアビット(図 5 の例では FF5、FF6)を X にすることが可能となる.

## 4 テストパターン数削減指向制御ポイント挿入法 4.1 制御ポイントの構造

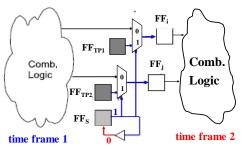

文献 [13] での制御ポイントは、マルチプレクサとスキャン FF から構成されている。図 6 に制御ポイントの構造を示す。制御ポイントは元の回路のスキャン FF の入力に付加される。図 6 の FFi、FFi は元回路のスキャン FF を示し、FFrp1、FFrp2、FFs は制御ポイント挿入により付加されたスキャン FF を示している。FFs ではマルチプレクサを制御しており、1 時刻目では制御ポイントからテストパターンを印加し、2 時刻目では組合せ回路からの回路応答をテストパターンとして印加可能となっている。

## 4.2 制御ポイント挿入箇所探索アルゴリズム

遷移故障を検出するためのテストパターン数を削減するためには制御ポイントを挿入する箇所が重要となる。そこで今回は制御ポイント挿入箇所探索アルゴリズムを提案する、提案する制御ポイント挿入箇所探索アルゴリズムでは、ATPGを1回しか行わず、テスト圧縮の観点から遷移故障のテストパターン数を削減するような制御ポイント挿入箇所を探索する。

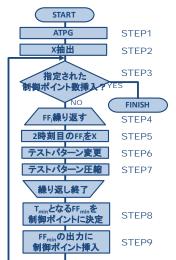

図7に制御ポイント挿入箇所探索アルゴリズムを示す. STEP1では,遷移故障用のテストパターンを生成する. STEP2では,生成されたテストパターンに対して,

図 6. 制御ポイントの構造

図 7. 制御ポイント挿入箇所探索アルゴリズム

X 抽出[18]を行う、STEP3 では、任意に指定した制御 ポイント数分制御ポイントが挿入されたか判断を行う. 制御ポイントが挿入されていれば処理を終了し、され ていなければ STEP4~STEP9 までの処理を行う. STEP4~STEP7では、回路中すべてのスキャンFF に対して評価尺度を用いて最適な制御ポイント挿入箇 所か評価を行う. STEP4 では、制御ポイント挿入を行 うスキャン FF を一つ選択する. STEP5 では, 選択し たスキャン FF の 2 時刻目のテストパターンの値を X にする. STEP6 では、選択したスキャン FF の 2 時刻 目のテストパターンをXにしたことによる影響を考慮 し、1時刻目のテストパターンの値を X に変更する. このとき、テストパターンでの故障検出数が変化しな いようにテストパターン変更を行う. STEP7 では、 STEP6 で変更したテストパターンに対して静的圧縮 [19]を行う. このとき, 頂点彩色アルゴリズム[20]を 用いて静的圧縮を行う. STEP8 では, 評価尺度より計 算したスキャン FF の評価値が最大となるものでなお かつテストパターン数が最小となるものを制御ポイン ト挿入箇所と決定する. STEP9 では, STEP8 で決定 したスキャン FF に対して制御ポイント挿入を行う.

### 4.3 評価尺度

制御ポイント挿入箇所探索アルゴリズムの評価尺度を式(1)に示す.  $\mathbf{v}$ は $\{0, 1, X\}$ からなる論理値を表し、 $\mathbf{ttp}$  は遷移故障のテストパターンを表している.  $\mathbf{stf}$  はスキャン  $\mathbf{FF}$  を表し、 $\mathbf{ssf}$  は各時刻におけるスキャン  $\mathbf{FF}$  を表している.  $\mathbf{LVT}(\mathbf{stf}, \mathbf{ttp})$  は遷移故障のテストパターンで設定されるスキャン  $\mathbf{FF}$  の論理値を表している.  $\mathbf{J}(\mathbf{stf}, \mathbf{v})$  は  $\mathbf{stf}$  の論理値を  $\mathbf{v}$  に正当化するために必要なスキャン  $\mathbf{FF}$  の集合を表している. 式(1)の評価尺度では、すべてのテストパターンにおいて割当てられた  $\mathbf{2}$  時刻目のスキャン  $\mathbf{FF}(\mathbf{stf})$  の値  $\mathbf{0}$  と  $\mathbf{1}$  を正当化するときに必要となるスキャン  $\mathbf{FF}$  集合数の累計数が最も多い  $\mathbf{stf}$  を制御ポイント挿入箇所とする.

$$\max_{sff \in SFF} \left( \sum_{ttp \in TTP} \left( |J(sff_2, LVT(sff_2, ttp))| \right) \right)$$

(1)

## 5 予備実験

予備実験として ISCAS'89 ベンチマーク回路の 7つ (s5378,s9234,s13207,s15850,s35932,s38417,s38584) に対して実験を行った. 元回路において, 遷移故障検出用テストパターン数と故障検出率がどのようになるのか実験を行った. 表 1 に元回路において遷移故障用テストパターン数と遷移故障検出率を示す. CIR は回路名, TP はテストパターン数, FC は故障検出率を表す

元回路において遷移故障用のテストパターンを生成した結果が表1のようになった.提案した制御ポイント挿入箇所アルゴリズムを用いることによって、故障検出率を維持しながらテストパターン数が削減できると考えられる.しかしながら、制御ポイント挿入をすることで回路中の面積オーバーヘッドが増加する.また、制御ポイント挿入とテストパターン数は、トレードオフの関係にあるので制御ポイント挿入の個数を考慮することも重要である.

表 1. 予備実験

|        |      | Original |       |

|--------|------|----------|-------|

| CIR    | FF   | TP       | FC(%) |

| s5378  | 179  | 186      | 91.05 |

| s9234  | 228  | 326      | 84.67 |

| s13207 | 669  | 314      | 82.16 |

| s15850 | 597  | 206      | 73.05 |

| s35932 | 1728 | 67       | 84.63 |

| s38417 | 1636 | 238      | 98.70 |

| s38584 | 1452 | 367      | 87.64 |

## 6 予備実験

遷移故障におけるテストパターン数を削減するような箇所に制御ポイントを挿入するための評価尺度と制御ポイント挿入箇所探索アルゴリズムを提案した.

今後の予定としては、評価尺度の改善、制御ポイント挿入箇所探索アルゴリズムの改善を行う.

#### [参考文献]

- [1] H.Fujiwara, Logic Testing and Design for Testability, The MIT Press,1985.

- [2] M Abramovici, M.A.Breuer and A.D.Frindman, Digital Systems Testing and Testable Design, Computer Science Press, 1990.

- [3] International Technology Rodemap for Semiconductors 1999 Edition, Semiconductor Industry Association, 2005

- [4] A.Krstic and K.-T.Cheng, "Delay Fault Testing for VLSI Circuits", Kluwer Academic Publishers, 1998.

- [5]Y.Takamatsu, T.Shiosaka, T.Yamada and K.Yamazaki, "A Fault Model and Test Generation for Bridging Faults in CMOS Circuit", IEICE Trans., Vol.J81-D, No.6, pp.872-879, Jun.1998.

- [6] Chih-chang Lin, Marek-Sadowska, Kwang-Ting Cheng and Mike Tien-Chien Lee, "Test Point Insertion:Scan Paths through Combinational Logic", 33rd Design Automation Conference, 1996.

- [7] M.J.Geuzebroek, J.Th.van der Linden and A.J.van de Goor, "Test Point Insertion for Compact Test Sets", Pros. Int. Test Conf., PP. 292-301, 2000.

- [8] I.Pmeranz and S.M. Reddy, "Test-Point Insertion to Enhance Test Compaction for Scan Designs", Dependable Systems and Networks, PP. 375-381, June 2000.

- [9] M.J.Geuzebroek, J.Th.van der Linden and A.J.van de Goor, "Test Point Insertion that facilitates ATPG in reducing test time and data volume", Pros. Int. Test Conf., PP. 138-147,2002.

- [10]吉村正義, 細川利典, 大田光保, "テストパターン 数削減指向テストポイント挿入方法", 信学論, vol. J86-D-I, no. 12, PP. 884-896, 2003.

- [11]Santiago Remersaro, Janusz Rajski, Thomas Rinderknecht, Sudhakar, M. Reddy and Irith Pomeanz, "ATPG Heuristics Dependant Observation Point Insertion or Enhanced Compaction and Data Volume Reduction", IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, 2008.

- [12]Seongmoon Wang and Srimat T. Chakradhar, "A Scalable Scan-Path Test Point Insertion Technique to Enhance Delay Fault Coverage for Standard Scan

- Designs", IEEE Transactions on Ransactions on Computer-Aided Design of Integerated Circuits And Systems,vol.25, No.8, August 2006.

- [13]Kedarnath J. Balakrishnan and Lei Fang, "RTL Test Point Insertion to Reduce Delay Test Volume", IEEE VLSI Test Symposium, 2007.

- [14]J.Savir. ,"Skewd-Load Transition Test: Part 1: Calculaus.", Proceedings of IEEE International Test Conference, PP.705-713, October 1992.

- [15]J.Savir. ,"Skewd-Load Transition Test: Part 2: Calculaus.", Proceedings of IEEE International Test Conference, PP.714-722, October 1992.

- [16]J. Savir and S. Patil "On Broad-Side Delay Test" VLSI Test Symposium., pp.284-290 Sept. 1994.

- [17]L.H.Goldstain, "Controllability/Observability analysis of digital circuits, "IEEE Trans. Circuits Syst., bol.CAS-26, no.9, pp.685-693, Step.1979.

- [18]Kohei Miyase and Seiji Kajihara, Irith Pomeranz, "XID: Don't Care Identification of Test Patterns for Combinational Circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 23, No. 2, pp. 321-326, Feb. 2004.

- [19]Niraj jha and Sadeep Gupta,"Testing of Digital Systems", Cambridge university Press, 2002.

- [20]八木澤圭,山崎浩二,細川利典,玉木久夫"テストパターンの静的圧縮における厳密解と貪欲解の比較",電子情報通信学会技術研究報告,PP. 77-82,2008.