# BASTアーキテクチャにおける擬似ランダムパターンの反転数削減のための決定的パターンのマッピング法

ーマッピングアルゴリズムの違いによる反転数の比較ー

日大生産工(院) ○万 玲玲 日大生産工 細川 利典

#### 1 はじめ

近年、半導体技術の急速な進歩により、LSIの回路規模が増大し、回路構造もより複雑化している。一般的にLSIの論理部のテストを行うにはスキャン設計と自動テスト生成ツール[1] (Automatic Test Pattern Generator: ATPG) によるテスト生成が広く受け入れられてきた。このテスト手法によって高い故障検出効率が得られるが、回路の高集積化に伴いATPGにより生成されたテストパターン数が増大し、テストデータ量がテスタのメモリをオーバーフローするような問題が発生し、テストデータ圧縮技術の重要性が一気に高まってきた。

そこで、考案されたものに組込み自己テスト

[1] (Built-In - Self - Test: BIST) とATPGを用いて生成した高い故障検出率のテストパターン集合を組み合わせた技術がある.この技術はテストデータ量の圧縮と設計フローへの影響をなくし、さらに高い故障検出効率のテストパターンを得ることを目的としている.これらの技術の1つとして組込み自己テスト援用スキャンテスト (BIST Aided Scan Test: BAST)[1]が挙げられる.BASTに代表される擬似ランダムパターン生成器から生成される擬似ランダムパターンのあるビットを反転させ、ATPGから生成される決定的パターンに変換し、テストを行う技術[3]はATPGのテストパターンを利用できることにより、高い故障検出効率が実現できる.

本稿では、BASTアーキテクチャによる擬似ランダムパターンの反転数を削減するための決定的パターンのマッピングアルゴリズムを実装し、評価する。第2章では、BASTの基本概念について説明する。第3章では、BASTアーキテクチャについて説明する。第4章では、BASTテストパターン[1]の生成方法について説明する。第5章では、擬似ランダムパターンの反転数を削減するための決定的パターンとのマッピングアルゴリズムについて説明する。第6章では、実験結果につい

て述べる. 第7章では、本稿のまとめについて述べる.

#### 2 BAST基本概念

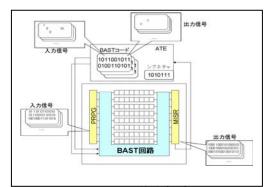

BASTの基本概念は「ATPGにより生成される決 定論的テストパターンは全てのビットを指定す ることない」という事実に基づいている. 多く の場合、決定論的テストパターンは大多数のド ントケアビット及び少数のケアビットから構成 されている. ここで外部入力に1または0の割 り当てがされたビットをケアビット,外部入力 に値が割り当てされていないビットをドントケ アビットと呼ぶ.ケアビットの割合は通常1% ~5%で、このケアビットの値が故障検出に必 要な値となる. 図1はBASTの基本概念図である. 基本構成は、 擬似ランダムパターンを発生する 擬似ランダムパターン生成器PRPG[1] (Pseudo Random Pattern Generator) と出力信号をシ グネチャに圧縮するMISR[1](Multiple Input Signature Register)を持つBISTである. ATPG により割当てられる擬似乱数の値はPRPGにより テスト回路内部で生成される. よって, テストデ ータの大部分は、この他にBASTコードと呼ばれ る入力用のテスト系列や期待値を格納するテス タ[5] (Automatic Test Equipment: ATE) とCUT 間のインタフェースチャンネルを通して印加さ れる. 決定的テストパターン中のドントケアビ ットの値はPRPGを用いてCUT内部のスキャンチ ェインに割り当てられるため、テストデータの 大部分はATEのメモリから除外される. ケアビッ トの値はATEとCUT間のインタフェースチャネル を通してコード化されて印加される. 更にMISR によってATE中にすべての出力期待値を記憶す る必要性をなくす. MISRの利用は、シグネチャを 取り組むときのアンノウン(X)状態の問題を取 り扱うことが必要となり、BASTは、アンノウン (X)状態の影響をマスクする機能ももつ.

## A Mapping Method of Deterministic Patterns to Reduce the Number of Flips for Pseudo Random Random Patterns Lingling Wan, Toshinori HOSOKAWA

図1. BAST基本概念図

#### 3 BASTアーキテクチャ

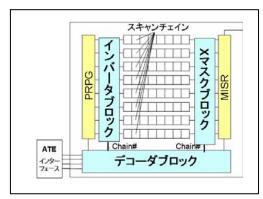

BASTアーキテクチャは、一般的なスキャンベースBIST STUMPS (Self-Test Using a MISR and a Parallel Shift register sequence generator) [5] に基づいている。BAST用のテスト回路論理はスキャンチェインの入力とPRPGインバータブロック、スキャンチェインの出力とMISRの間に挿入され、図2に示すようにデコーダブロックを加結し、三つのブロックから構成される。

図2. BASTアーキテクチャ

#### 3.1 インバータブロック

インバータブロックはPRPGの出力とスキャンチェンインの入力の間に置かれる.これは、PRPGからスキャンチェンインへ通過する信号を反転させる.図3はインバータブロックの1ビット分の論理を示す.インバータブロックは、スキャンチェンイン数と同一のビット幅を持つ.その論理はXORゲートから構成され、反転を制御するフリップフロップ(FF)の信号に従いPRPGの出力信号の反転操作を行う.なおFFの入力Set、Resetにより反転制御を行い、Setが1かつResetが0の時は反転を設定し、Resetが1かつSetが0の時は擬似ランダムテストパターンの値をそのまま出力するように設定する.

### 3.2 Xマスクブロック

Xマスクブロックは、内部スキャンチェンイ

ンの出力とMISRの入力の間に置かれる.図4はXマスクブロックの1ビット分の論理を示す.Xマスクブロックもインバータブロックと同様にスキャンチェイン数と同一のビット幅を持つ.その論理はORゲートで構成され,マスク制御用のFFによりX状態をマスクする.なおFFの入力Set, ResetによりXマスク制御を行い,Setが1かつResetが0の時はマスク操作が設定され,Resetが1かつSetが0の時はスキャンチェインからの出力値をそのままMISRに出力するように設定する.

#### 3.3 デコーダブロック

デコーダブロックは、コード化された信号を受け取るインタフェースチャネル(インバータブロックの反転を制御するインバータフラグ信号とXマスクブロックを制御するXマスクfラグ信号及びスキャンチェンインを選択するための複数のチェンインアドレス信号から構成される)に接続され、インバータブロック、Xマスクブロックの対応するFFを制御する.

#### 3.4 BASTコード

インタフェースチャネルで、インバータブロックの反転を制御するインバータフラグ信号と、Xマスクブロックを制御するXマスクフラグ信号、及び、スキャンチェインを選択するための複数のチェインアドレス信号から構成される.インタフェースチェネルに入力されるコード化されたテストパターンをBASTコードと呼ぶことにする.

# 4. BASTにおけるテストパターンの生成方法

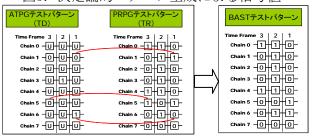

BASTにおけるテストパターン生成について 述べる. 決定的テストパターン生成によりCUT のテストパターンを生成し,同時にLSI内部に 埋め込まれたPRPGが生成するものと同一の擬 似ランダムパターン(TR)を生成する. これらの テストパターンを重ね合わせた,回路に印加さ れるテストパターンをBASTテストパターンと 呼ぶ. 以下はBASTテストパターンについて説明 する. 図3はスキャンチェイン8本, スキャンチ ェイン長がそれぞれ3のときに、決定的テスト パターンに (TD) おけるFFの信号割り当ての例 を示す. 図中の0.1はケアビッドの入力信号 値, Uはドントケアビッドの状態を示す. 図4は TDとTRの各対応するビット位置を重ね合わせ る.BASTテストパターンを次のように決定する. 図7は、右側に図6で示しスキャンチェインを構

成するFFに対し、擬似乱数で設定された信号値が割り当てられた状態を示し、左側に決定的パターン生成からのケアビットの入力信号値のみ書き出したものを示す。すべてのタイムフレーム(t=1~3)、すべてのスキャンチェイン(i=0~7)に対して以下のステップを操作する。

- 1) タイムフレームt, チェインiのビット位置 におけるTDの値がU状態ならば, BASTテス トパターンの信号値はTRの信号値をとる.

- タイムフレームt, チェインiのTDの信号値 がTRの信号値と一致ならば, BASTテストパ ターンはTRの信号値をとる。

- 3) タイムフレームt,チェインiのTDの信号値 がTRの信号値と不一致ならば,BASTテスト パターンはTDの信号値をとる.

図3. 決定論的パターン生成による信号値

図4. 入力信号の重ね合わ 図5. BASTテスト パターン

また,図5は生成されたBASTテストパターン を示す.

#### 5. マッピングアルゴリズム

BASTコード量やテスト実行時間を削減するため、BASTアーキテクチャにおける擬似ランダムパターンの反転数の削減のための決定的パターンとのマッピング法について検討する.

#### 5.1 マッピングアルゴリズム

文献[1]で提案されているマッピングアルゴリズムを検討する.このアルゴリズムは評価関数を用いて,決定的パターンと擬似ランダムパターンのマッピングを行う.また,この評価関数は3つのポリシーによって,定義される.

1) ビット反転数の多い擬似ランダムパター ンはマッピングしない.

- 2) ビッド反転数が少ない擬似ランダムパタ ーンが複数ある場合,決定的パターンの マッピングの優先度が低い.

- 3) ビッド反転数が最小のランダムパターン とビッド反転数が2番目に少ないランダ ムパターンは決定的パターンとのマッピ ング優先度は高い.

よって,評価関数W(i)は式(1)のように示す.

$W(i) = (Y_{gamma_i} - Y_{alpha_i}) + (Y_{beta_i} - Y_{alpha_i})$ (1)

W(i)は決定的パターンに対して、擬似ランダムパターンとマッピングするときの優先度を表している、W(i)は大きければ大きいほど先にマッピングされる。また¥alpha\_iは決定的パターンに対して、最小ビット反転数と定義する。 ¥beta\_iは決定的パターンに対して、2番目最小ビット反転数と定義する。¥gamma\_iは決定的パターンに対して、最大ビッド反転数と定義する。

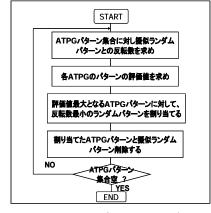

図6にマッピングアルゴリズムを示す.まず,決定的テストパターン集合中の全てのパターンに対し,擬似ランダムテストパターンとの反転数を求める.反転数を用いて,評価関数に基づき,各決定的パターンの評価値を計算する.次に,評価値最大となる決定的パターンに対して、反転数最小の擬似ランダムパターンを割り当てる.割り当てた決定的パターンと擬似ランダムパターンに対し削除する.これらの一連の処理が決定論的パターン集合を Ø となるまで繰り返す.

図6. マッピングアルゴリズム

#### 5 実験結果

今回評価する実験データは、*ISCAS' 89*ベンチマーク回路のs35932、s38584及び*ITC' 99*ベンチマーク回路を用いる.スキャンチェインに数が16とした.決定的パターンと擬似ランダムパターンを先頭から順にマッピングするアルゴリズムと本稿で述べた文献[1]のマッピング

アルゴリズムを実装し、擬似ランダムパターンのビット反転数を評価した.表1において、 Circuitは回路名、#Flip Flopは回路内のフリップフロップ数、#ATPG patternsはATPGのテストパターン数を示す.

表1 決定的パターン数

| 21 200 200 200 200 |            |                |  |  |  |

|--------------------|------------|----------------|--|--|--|

| Circuit            | #Flip Flop | #ATPG patterns |  |  |  |

| s35932             | 1763       | 21             |  |  |  |

| s38584             | 1462       | 147            |  |  |  |

| b15                | 485        | 453            |  |  |  |

また、表2において、Cirは回路名、prpgseed は擬似ランダムパターン生成器の種、#ori\_flip\_numは単純マッピング法のビット反転数、#new\_flip\_numは反転数削減マッピング法のビット反転数、num\_rrは回路ビット反転数の削減率を表す.回路ビット反転数の削減率は式(2)により求められる.

$num\_rr = \frac{\#ori\_mathod\_flip\_num-\#new\_mathod\_flip\_num}{\#ori\_mathod\_flip\_num} \times 100 (2)$

表 2 反転数削減率

| Circuit | prpgseed | #ori_flip_num | #new_flip_num | num_rr(%) |

|---------|----------|---------------|---------------|-----------|

| s35932  | 10       | 18682         | 18140         | 3.00      |

| s38584  | 10       | 107491        | 102406        | 4.73      |

| b15     | 10       | 109972        | 97313         | 11.5      |

表2から、BASTアーキテクチャに基づいて、擬似ランダムパターン生成器の種を二進数の10で与え、単純マッピング法と反転数削減マッピング法でのマッピンで反転数削減率は3%~11.5%程度であった。よって、回路全体のBASTコード量を削減することができた。

#### 6 まとめ

本稿では、テストデータであるBASTコード量を削減するために、BASTアーキテクチャにおける擬似ランダムパターンの反転数を削減するための決定的テストパターンのマッピングアルゴリズムを実装、評価し、BASTコード量が削減できることを確認した.

今後の課題として,決定的パターンとの反転 ビットが少なくなるようなテストポイント挿 入法を提案する.

#### 「参考文献」

[1] Masayuki Arai, Satoshi Fukumoto, Kazuhiko Iwasaki, Takahisa Hiraide, Takashi Aikyo," Test Data Compression Using TPG Reconstruction for BIST-Aided Test", proc. IEEE 6<sup>th</sup> Workshop on RTL and High Level

Testing, 211-8588, 2005.

- [2] 相京 隆, 平出 貴久, 江守 道明," BAST:Bist Aided Scan Test-テストコスト削減のための新しい手法",電子情報通信学会論文誌, Vol. J88-D-I, No. 6, pp. 1012-1020, 2004. 8. 27.

- [3] 藤原 秀雄,"ディジタルシステムの設計とテスト",工学図書株式会社.

- [4] 武内 和志,"組込み自己テスト援用スキャンアーキテクチャによるテストデータ圧縮に関する研究",卒業論文,2006.

- [5] P. H. Bardell and W. H. McAnney," Parallel pseudo-random sequences for built-in test," Proc. ITC, pp. 302-308, 1984.