# ソフトエラー対策の為の CPU キャッシュメモリ多重化に関する評価

日大生産工(学部) o川島 直也 日大生産工 新井 雅之

# 1. はじめに

近年,LSIの高速化や微細化に伴い,ソフトエラー耐性の重要性が認識されるようになってきた[1][2].また,宇宙開発が活発化し,商業用のシステムを宇宙環境に配備する計画が増えてきた.宇宙環境では,地上よりも宇宙線の影響を受けやすい為,アプリケーションのソフトエラーを引き起こす可能性がある.その中でも特にキャッシュメモリに対し,誤動作が多いとの報告がある[1].

本研究では、CPUキャッシュメモリの多重化 手法に基づく高信頼設計に対して、性能、コスト、信頼度をトレードオフの観点から評価する. 性能は、プロセッサシミュレータを使用し、キャッシュメモリサイズを変化させた場合の実行サイクル数を測定する.

## 2. 関連研究

# 2-1. キャッシュメモリ

キャッシュメモリは、CPUとメインメモリの中継を行い、命令やデータの高速処理を実現する. プログラムを格納し、やり取りを行う命令(I) キャッシュや、処理するデータを格納し、やり取りを行うデータ(D) キャッシュが存在する. これらは、合わせて共通キャッシュとして存在する場合もあるが、それぞれを最適化し、分離化したものも存在する. また、CPUに近いキャッシュから、L1(レベル1) キャッシュ、L2(レベル2) キャッシュと呼ばれる.

# 2-2. ソフトエラー

ソフトエラーは、LSIの何らかの原因によって引き起こされる、一時的な誤動作である。宇宙線などの放射線によって起こる不具合や誤動作をSEE (Single Event Effect)と呼ぶ。SEEには複数種類があり、回路周辺に粒子線が通過し、一時的に電圧パルスが生じるSET (Single Event Transient)や、粒子線通過時に発生する電

荷・電流によって一時的にデータが反転してしまうSEU (Single Event Upset) がある.

# **2-3.** レーザテスティングによるプロセッサへの故障挿入

Waltersらのレーザテスティングは、実際のPowerPCに、可動式のレーザを照射するによって、擬似的に宇宙線による故障を再現し、エラーがどこで発生したのかを再現する[1]. この実験によって、2000回以上の故障挿入を経て、エラーの多くが、キャッシュメモリ上で発生していることが報告された.

# 3. プロセッサシミュレータを利用した 性能算出及び解析的評価

キャッシュメモリ多重化の評価に際しては, 性能,コスト,信頼度のトレードオフを考慮す ることが重要である.本稿は,その中でも性能, コストの2点に着目して実験を行った.

#### 3-1. 性能評価の概要

性能測定の為に、プロセッサシミュレータの鬼斬弐を使用し、キャッシュサイズを変更して評価を行った[3]. 鬼斬弐は、サイクル毎のプロセッサ挙動を再現できるプロセッサシミュレータである.

本稿では、鬼斬弐のデフォルトに用意されているプロセッサモデルの Alpha を利用した. Alpha は 64bit の RISC 命令セットアーキテクチャである. Alpha 用にコンパイルしたプログラムをセットし、実行することによって、プロセス毎のメモリ消費量や CPU におけるクロックあたりの実行数等を知ることができる.

特定のヘッダプログラムを変更することで、キャッシュサイズなどの鬼斬弐のデフォルト値を変更することができる. ヘッダファイルの IndexBitSize を減少させ、出力される Executed Cycles の値によってプロセッサの性能を測定

Evaluation of CPU Cache Multiplexing for Soft Error Mitigation

Naoya KAWASHIMA and Masayuki ARAI

する実験を行った.

鬼斬弐にセットするプログラムとして,線形合同法によって生成した乱数を,50個の配列に格納し,クイックソートによって降順に並び替え,画面出力し,実行させるものをC言語で作成した.

## 3-2. 性能評価結果

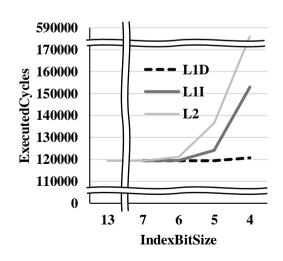

今回使用した Alpha 内のキャッシュメモリには、CacheL1D(レベル1データキャッシュ)、CacheL1I(レベル1命令キャッシュ)、CacheL2(レベル2共通キャッシュ)の3種が存在する. これらの IndexBitSize の値を変更し、測定した Executed Cycles の結果を表1に示す.

Index はキャッシュのブロックを選択するために使用されるものであり、Index 総数(キャッシュサイズ)は IndexBitSize の値に関係がある。表 1 で網目となっているセルは、それぞれのキャッシュメモリの IndexBitSize のデフォルト値であり、CacheL1D と CacheL1I は 7 ビット、CacheL2 は 13 ビットに設定されている。デフォルト値のキャッシュサイズは、それぞれ  $2^7$ 、 $2^{13}$ である。従って IndexBitSize の値を 1 減らす毎に、キャッシュサイズは半分になる。

IndexBitSize を小さくした場合, CacheL1D (CacheL1D の 6 は除く), CacheL1I キャッシュのそれぞれで実行サイクル数の増加が確認できた. しかし, CacheL2 では IndexBitSize を減少させても, 実行サイクルは増加しなかった. キャッシュサイズを半分にする毎に, 一つ当りの Executed Cycles が増え, 負荷がかかることがわかる. 特に, キャッシュレベルが上がる毎に, また, データキャッシュよりも命令キャッシュの負荷がより大きいことがわかる.

#### 4. まとめ

本研究では、キャッシュメモリの多重化における、評価を目的として、キャッシュメモリサイズを変化させた場合の実行サイクル数の測定を行った.性能に関しては、キャッシュサイズを一定以上減らすと、Executed Cyclesが増加し、負荷がかかることが確認できた.

今後は、信頼度の解析的評価を組み込むことで、更なる高信頼化における評価付けが行えることと考える.

# 参考文献

[1] J. P. alters, K. M. Zick, and Matthew French,

- "A practical characterization of a NASA SpaceCube application through fault emulation and laser testing," Dependable Systems and Networks, 2013 年.

- [2] 戸坂義春, "LSI 信頼性向上のための宇宙 中性子ソフトエラー解析シミュレータ," 雑誌 FUJITSU, Vol.51, No. 5, pp. 303-307, 2000 年.

- [3]塩谷亮太,五島正裕,坂井修一,"プロセッサ・シミュレータ「鬼斬弐」の設計と実装,"情報処理学会シンポジウム論文集,2009 巻,5号,pp120-121,2009年.

表 1. 各キャッシュメモリの IndexBitSize 毎の Executed Cycles

| DACCULCU Cycles |         |          |

|-----------------|---------|----------|

| Type of         | Index   | Executed |

| Cache           | BitSize | Cycles   |

| L1D             | 7       | 119390   |

|                 | 6       | 119390   |

|                 | 5       | 119402   |

|                 | 4       | 120765   |

| L1I             | 7       | 119390   |

|                 | 6       | 119547   |

|                 | 5       | 124199   |

|                 | 4       | 152977   |

| L2              | 13      | 119390   |

|                 | 7       | 119390   |

|                 | 6       | 121165   |

|                 | 5       | 136573   |

|                 | 4       | 589283   |

図 1. 各キャッシュメモリの IndexBitSize 毎の Executed Cycles 変化グラフ