## 予備タイルを追加したアンバイポーラ素子の

## Sea-of-Tiles における耐故障設計および評価

日大生産工(院) ○高橋 暖 日大生産工 新井 雅之

### 1 まえがき

CMOS 集積回路の縮小化の鍵であるMOSFETの微細化において、シリコンナノワイヤ(SiNW)構造や、新たにゲート電極を追加してアンバイポーラとし回路設計を効率化するなどの研究が行われている[1,2]. また、ICの歩留り向上のための技術として、Sea-of-Tilesと呼ばれる、小規模な基本ゲートをチップ上に敷き詰めた規則的なレイアウトに基づく回路設計の研究も行われている[3]. しかし、これらの技術を使用する際の冗長化については、あまり検討されていない.

本研究ではアンバイポーラ素子のSea-of-Tilesレイアウトにおいて予備タイルを追加した冗長化構成を提案する.提案手法では、故障した論理ゲートを隣接タイルで再構成する.また、冗長化構成において使用するマルチプレクサ(MUX)を削減する方法についても提案する.LTspiceで動作確認を行い、使用トランジスタ数を評価する.

# 2 アンバイポーラ素子のSea-of-Tiles構造

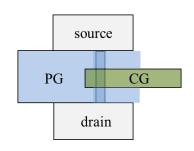

アンバイポーラ素子は従来のMOSFETでは1個だったゲート電極を2個持ち、従来のゲート電極と、新たに追加したゲート電極(PG)に電圧を印加することによってn型、p型を切り替えて使用することが出来る[1-3].

図1 アンバイポーラ素子

図1にアンバイポーラ素子を示す. CGは従来のゲート電極に相当する.

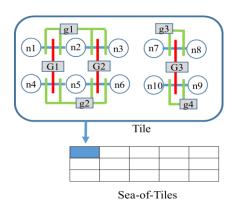

Sea-of-Tilesは、いくつかのアンバイポーラ素子から構成されたタイルを規則的に敷き詰めたものである。図2に、本研究で用いるタイルの内部構成およびSea-of-Tilesを示す。G1、G2はCGとなるゲート電極であり、g1、g2はPGとなるゲート電極である。n1~n10はソース・ドレーンまたは入出力端子となっている。端子への信号線入力パターンを変えることで、様々な論理ゲートを構成することが可能である[3].

図2 タイルおよびSea-of-Tiles

## 3 Sea-of-Tilesの冗長化及び動作シミュレーション

#### 3.1 冗長化手法の概要

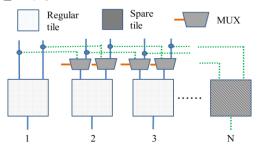

Sea-of-Tilesに対する冗長化手法を提案する. 提案手法では、並列に並んだタイルの最終段に 予備タイルを1個追加する.タイルに入力され る信号線を取り出し、取り出した入力と隣接タ イルの通常入力をマルチプレクサに接続する. 図3にSea-of-Tilesの冗長化構成を示す.並列な タイルの内1個が故障しても、隣接するタイル で再構成されるためマスクすることが可能と なる.また、出力信号線が混線しないようにす

Spare-Tile-Based Dependable Design and Evaluation for Sea-of-Tiles Architecture of Ambipolar Devices

Dan Takahashi and Masayuki Arai

るためにいくつかの端子にはスイッチが必要である.ここでのマルチプレクサは4トランジスタのトランスミッションゲートで実現している.本稿ではマルチプレクサの故障判定信号の生成方法については考慮しておらず,今後の課題である.

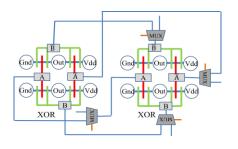

図3 Sea-of-Tilesの冗長化構成

#### 3.2タイル配置を考慮した冗長化

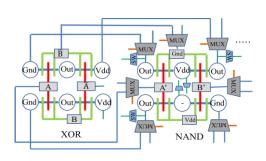

タイル配置を考慮せず、全端子、ゲート電極への入力を隣接タイルのマルチプレクサに接続した場合、マルチプレクサ、スイッチの使用数が増大してしまう。そこで、論理ゲートを考慮したタイル配置を提案する。この手法では、回路設計の段階でSea-of-Tiles上に同一な論理ゲートを構成するタイルが隣接するように設計する。論理ゲートを考慮しない場合、した場合のタイル配置を図4に示す。XOR、NANDゲートのタイルを並べた場合では、XORゲート故障時にNANDゲートを構成するタイルがXORゲートを再構成するため、9個のマルチプレクサ、5個のスイッチが必要となる。

(a) 単純なタイル配置

(b)論理ゲートを考慮したタイル配置

#### 図4 論理ゲートを考慮したタイル配置

一方,同一な論理ゲートを構成するタイルが隣接する配置では,冗長化する信号線が論理ゲートへの入力だけとなるため,スイッチは必要なく,マルチプレクサも4個に抑えることが可能となる.

#### 3.3 動作およびトランジスタ数の評価

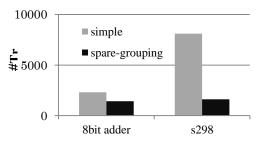

動作確認として、spiceシミュレーション上でタイルを構成し、故障時の動作を確認した.ただし、アンバイポーラ素子のspiceモデルは著者らの知る限り提供されていないため、機能的等価モデルを用いている.また、トランジスタ数の削減の観点から論理ゲートを考慮したタイル配置の有効性を評価した.図5に8ビット全加算器とISCAS'89 s298ベンチマーク回路のトランジスタ数の結果を示す. simpleは、論理ゲートを考慮しないタイル配置であり、spare-groupingは、考慮したものである。8ビット全加算器では38%、s298では、より多くのトランジスタを減らす結果となった.

図5 使用トランジスタ数の比較

#### 4 まとめ

本稿ではSea-of-Tilesの冗長化手法について 提案し、トランジスタ数の評価を行った. タイル配置を考慮するSea-of-Tilesでは、単純なもの と比較し有用性が確認された. またさらなる削減のためにnMOS単体によるスイッチの実装 に取り組んでいる.

#### 参考文献

- [1] M. Haykel Ben-Jamaa, K. Mohanram, G. De Michel, "An Efficient Gate Library for Ambipolar CNTFET Logic," IEEE Transactions on Computer-Aided Dessign of Integrated Circuits and Systems, Vol. 30, No. 2, pp. 242-255, 2011.

- [2] 岩井洋, 角嶋邦之, "シリコンナノワイヤFET技術," 電子情報通信学会誌, Vol.95, No. 4, pp. 278-283, 2012年.

- [3] S. Bobba, M. De Marchi, Y. Leblebici, G. De Micheli, "Physical Synthesis onto a Sea-of-Tiles with Double-Gate Silicon Nanowire Transistors," Proceedings of the 49th Annual Design Automation Conference, pp. 42-47, 2012.