# ランダムパターンテスタビリティに基づくテストポイント挿入法

日大生産工部 〇万 玲玲 日大生産工 細川 利典 日大生産工(院) 斉藤 善洋

#### 1 はじめ

近年、半導体技術の急速な進歩により、LSI の回路規模が増大し、回路構造もより複雑化している。一般的に順序回路のテスト生成は困難であり、高い故障検出効率を達成するのは非常に難しい。そこで、高い故障検出効率を達成するテストパターンを生成するにはフルスキャン設計[1]に代表されるテスト容易化設計が必要である。しかし、その一方で回路中のゲート数に比例し、テストパターン数は増大している。これにともない、テスト実行時間が増大し、テストコストの増大につながっている。

そこで、テストコストを削減するための解決 策の一つとして、テストポイント挿入技術[1] が考えられる. 具体的には、テストポイント挿 入により、テストパターンの圧縮効率を上げる ことで、テストパターン数を削減する技術であ る.

本稿では、ランダムパターンテスタビリティ 解析に基づくテストポイント挿入法のテストパ ターン圧縮効率を評価する.また,組み込み自己 テストにおいて、ランダムパターンでの故障検 出率を向上させることを目的としたテストポイ ント挿入法が用いられている. ランダムパター ンのテスタビリティを評価する尺度として0.1 の生起確率を用いるCOPがある. 文献[2]はCOPを 用いてコスト関数を定義し, コスト関数の計算 値が小さくなる信号線にテストポイントを挿入 し, ランダムパターンでの故障検出率を向上さ せている. 第2章では、テストポイントの概要に ついて説明する. 第3章では, COPテスタビリティ 尺度とテストポイント挿入のためのコスト関数 について説明する. 第4章では、テストポイント 挿入アルゴリズムについて説明する. 第5章では, 実験結果について述べる. 第6章では、本稿のま

とめと今後の課題について述べる.

## 2 テストポイント

テストポイントとは、内部の信号線を可制御、可観測にするために挿入される論理回路のことである。ある信号線に、テストポイントを挿入することで、その信号線が直接外部から制御、観測できるようになる。現在提案されている多くのテストポイント挿入法は回路中のランダムなテスト容易性の改善を中心としたもので、回路中の故障のテスト容易性情報を必要とする。このテスタビリティ情報は、故障シミュレーションによって求められ、回路構造のテスタビリティ解析によって導き出され、その情報を用いてテストポイント挿入箇所が決定される。

本稿では、テストパターン数の削減を目的として、ランダムパターンテスタビリティ解析をCOP[2]に基づく可制御性、可観測性尺度を用いて行い、そのテスタビリティ情報を用いてテストポイント挿入箇所を探索する方法のテストパターン圧縮効率を評価する.

## 3 ランダムパターンテスタビリティ解 析

## 3.1 COPテスタビリティ尺度

COP [2] に基づくテスタビリティ解析は,可制御性[2]と可観測性[2]より導き出される.

可制御費 $C_l$ とは,ある信号線lを0(1)に制御する確率である.各信号線の可制御費は,回路の入力側から出力側へ計算される.また,外部入力においては,0と1の値を任意に設定することが可能である.したがって,0と1の値が等確率で発生すると考え,外部入力の0と1の可制御費はともに0.5とする.

A Test Point Insertion Method Based on Random Pattern Testability Lingling Wan, Toshinori HOSOKAWA and Yoshihiro SAITO 可観測費 $W_l$ とは、ある信号線lを可観測する確率である。また、外部出力POにおいては、直接観測できるので、可観測費は1とする。各信号線の可観測費を求めるとき、回路の出力側から入力側へ計算される。また、各ゲートに対してCOPテスタビリティ尺度計算式を表1に示す。表1において、2入力(または1入力) $X_1, X_2$ (または $X_1$ )のゲートの出力信号線をZとしたときのZの可制御費と $X_1$ の可観測費の計算式を示している。

表1 COP テスタビリティ尺度

| Gate | 可制御費 Cz             | 可観測h Wx 1  |  |  |

|------|---------------------|------------|--|--|

| AND  | Cx1 • Cx2           | Cx2•Wz     |  |  |

| NAND | 1-Cx1-Cx2           | Cx2 •Wz    |  |  |

| OR   | 1-(1-Cx1)*(1-Cx2)   | (1-Cx2)•Wz |  |  |

| NOR  | (1-Cx1)*(1-Cx2)     | (1-Cx2)•Wz |  |  |

| XOR  | Cx1+Cx2-2-Cx1-Cx2   | Wz         |  |  |

| NXOR | 1-Cx1-Cx2+2-Cx1-Cx2 | Wz         |  |  |

| BUF  | Cx1                 | Wz         |  |  |

| INV  | 1-Cx1               | Wz         |  |  |

#### 3.2 コスト関数

可制御費と可観測費を基に、各信号線における縮退故障が外部出力で検出される確率からコスト計算を行う. コスト計算[3]のための式を(1), (2), (3) に示す.

$Pd_{I/SAO(1)}$ は、信号線lにおける0(1)縮退故障の

$$Pd_{I/SAI} = C O_I \cdot W_I$$

$$= (1 - C_I) \cdot W_I$$

(1)

$$Pd_{I/SA0} = C1_I \cdot W_I \tag{2}$$

$$K = \sum_{l=1}^{L} (K_{1/SA_0} + K_{1/SA_1})$$

$$= \sum_{l=1}^{L} \left( \frac{1}{Pd_{1/SA_0}} + \frac{1}{Pd_{1/SA_1}} \right)$$

(3)

検出確率を表している。式(1)は信号線1にお ける1縮退故障を任意外部出力に検出するため には、信号線lの値を0に設定し、信号線lの値 を可観測しなければならない. したがって,  $Pd_{l/sal}$ はlの0可制御費と可観測費の積となる. また、式(2)は信号線 lにおける0縮退故障を任 意の外部出力で検出するためには、信号線1の 値を1に設定し、信号線lの値を観測しなけれ ばならない. したがって,  $Pd_{I/SA0}$  はlの1可制御費 と可観測費の積となる.  $_{K_{l/SAI(0)}}$ は信号線lにお ける1(0)縮退故障を検出するために,必要なコ ストとし、 $Pd_{I/SAI(0)}$ の逆数で定義する. すなわ ち, K<sub>I/SAI(0)</sub>は信号線lの1(0)縮退故障を検出する ために必要なランダムパターン数と考えるこ とができる.  $_{K}$  は各縮退故障を検出するコス トの総合であり、回路全体のコストである. Pd<sub>1/SAI(0)</sub>が大きいと、少ないランダムパターン

で故障を容易に検出することが可能である. 逆に、 $Pd_{I/SAI(0)}$ が小さいと、ランダムパターンによる故障検出が困難なため、大量のランダムパターンが必要となる.

## 3.3 コスト微分係数

微分係数式[3]を(4),(5)に示す.

$$\frac{dK}{dW_{i}}$$

可観測費による微分係数 (4)

$\frac{dK}{dC}$  可制御費による微分係数 (5)

式(4)は信号線*l*にテストポイント挿入することによって,可観測費が変化する信号線に与える影響率をCOP計算により表している.式(5)は信号線*l*にテストポイント挿入することによって,可制御費が変化する信号線に与える影響率をCOP計算により表している.これらの値は,テストポイント挿入箇所を決定するための指標として有効である.

## 4 コスト削減因子アルゴリズムによる テストポイント挿入アルゴリズム

ランダムパターンテスタビリティを改善するため,コスト削減因子(CRF: Cost Reduction Function)アルゴリズムによるテストポイント挿入法[3]を説明する.

ここで、CRFとは回路中の各信号線にテストポイント挿入することによりコストが減少する近似値を表している. CRF値を求める計算式を(5), (6), (7), (8)に示す

$$CRF_{l}^{AND} = \frac{1 - C_{l}}{2 - C_{l}} \cdot C_{l} \cdot \frac{dK}{dC_{l}} - \frac{2}{C_{l} \cdot (1 - C_{l}) \cdot W_{l}} \quad (5)$$

$$CRF_{l}^{OR} = \frac{C_{l} - 1}{C_{l} + 1} \cdot C_{l} \cdot \frac{dK}{dC_{l}} - \frac{2}{C_{l} \cdot (1 - C_{l}) \cdot W_{l}}$$

(6)

$$CRF_{l}^{OP} = (W_{l} - 1) \cdot W_{l} \cdot \frac{dK}{dW_{l}}$$

(7)

$$CRF_{l}^{OP} = (W_{l} - 1) \cdot W_{l} \cdot \frac{dK}{dW_{l}} - (\frac{1}{C_{l}} + \frac{1}{1 - C_{l}})$$

(8)

式(5),(6)はANDゲートによる0制御ポイント とORゲートによる1制御ポイントの挿入により 信号線のコスト減少分を表している.  $C_l$ は信 号線lにおける1の制御確率,  $W_l$ は信号線lに おける観測できる確率,  $\frac{dK}{dC_l}$ は信号線lにおけ

る可制御費の変化を表す.式(7)は信号線lに観測ポイント挿入することによる信号線lの

コスト減少分の近似値を表している。また、式 (8) は信号線l が外部出力であるときの観測ポイント挿入によるコスト減少分の近似値を表している。  $\frac{dK}{dW}$  は信号線l における可観測費の

変化を表す.テストポイント挿入候補に対して、 そのコスト減少値を求めるには、テストポイン トしたと仮定して、COPの再計算を行い、コスト値を求めるのが正確であるが、COP計算に時間がかかるため、CRFを用いて高速にコスト減少分の近似値を求める.

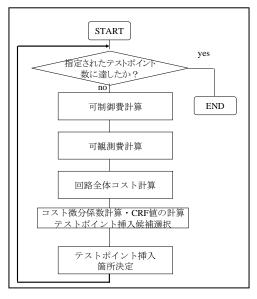

図1 CRFテストポイント挿入アルゴリズム

図1にCRFテストポイント挿入アルゴリズムを示す.まず,COP計算に基づき各信号線の可制御費,可観測費を計算する.可制御費と可観測費を基に,回路全体のコストを計算する.次に,信号線の可制御性と可観測性の変化によるグローバルコストへの影響を表す微分係数を用いて,各信号線にテストポイントを挿入することを仮定してCRF値を計算する.そのCRF値に基づきテストポイント挿入候補集合を決定する.回路中信号線のCRF最大値の10%以上である信号線を候補とする[4].各候補にテストポイント挿入によるCOP計算を再度行い,回路全体コストが一番小さいところをテストポイント挿入筒所とする.これらの一連の処理を指定されたテストポイント数が達するまで繰り返す.

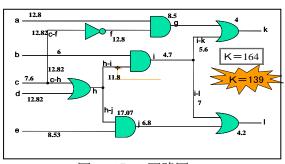

**例**. 図2の回路に対して、各信号線のコストを計算し、信号線h\_iに観測ポイントを挿入したときの回路全体のコストを比較する.

図2 c17aの回路図

図2の回路の信号線上に各信号線の0縮退と1縮退に対する値が示されている。各信号線のCRFを計算し、候補集合 $SLop=\{h_i,a,d,c_f\}$ が求められ、信号線 $h_i$ に候補に観測ポイントを挿入することによって、信号線のコストは11.7から3.436まで減り、全体コストKの値は164.0から139.0となり、ランダムパターンテスタビリティが改善されていることがわかる。

## 5 予備実験結果

今回評価する実験データは、ISCAS'85ベンチマーク回路に対して、ランダムテスタビリティ用のテストポイント挿入法をテストパターン圧縮[3]に用いて、テストポイント挿入前のコストを比較する.テストポイント挿入数は回路の全信号線数の1%とした.実験結果を表2に示す.表2において、Circuitは回路名、#COSTはテストポイント挿入前の回路コスト、#ACOSTはテストポイント挿入後の回路コスト、COST\_RRで回路コストの削減率を表す.回路コストの削減率は式(9)により求められる.

$$COST RR = \frac{\#COST - \#ACOST}{\#COST} \times 100$$

(9)

表 2 *ISCAS' 85*を用いた可検査性尺度 に基づくテストポイント挿入の結果

| Circuit | #COST           | #ACOST          | TPI(%) | COST_RR(%) |  |

|---------|-----------------|-----------------|--------|------------|--|

| c432    | 20447           | 58054           | 1      | -183.92    |  |

| c880    | 192498          | 201099          | 1      | -4.46      |  |

| c1355   | 6598577         | 6585194         | 1      | 0.21       |  |

| c1908   | 1302270         | 1412183         | 1      | -8.43      |  |

| c2670   | 106384175       | 428127          | 1      | 99.50      |  |

| c3540   | 15505416        | 11670778        | 1      | 24.73      |  |

| c5315   | 1662601         | 404501          | 1      | 75.62      |  |

| c6288   | 98863           | 88596           | 1      | 10.23      |  |

| c7552   | 186528726900191 | 125248655460874 | 1      | 32.21      |  |

COST\_RRの値からc432, c880, c1908はテストポイント挿入によって,逆にコストが増大してしまっている. これらの結果を解析するため, ATPGテストパターン生成に対するテストポイント挿入法[6]の実験結果を用いて,考察する.表3において, Cirは回路名, #TPはテストポイント挿入数(回路全信号線の1%とした), #CTはテストポイント挿入前のテストパターン数, #IFDTはテストポイント挿入後のテストパターン数を表す.

表3 *ISCAS' 85*を用いたテストポイント挿 入によるテストパターンの削減数の結果

| Cir   | #TP | #CT | #IFDP |

|-------|-----|-----|-------|

| c432  | 4   | 41  | 44    |

| c880  | 8   | 36  | 35    |

| c1355 | 13  | 100 | 117   |

| c1908 | 19  | 125 | 117   |

| c2670 | 27  | 72  | 51    |

| c3540 | 35  | 141 | 105   |

| c5315 | 53  | 92  | 52    |

| c6288 | 62  | 39  | 32    |

| c7552 | 75  | 117 | 79    |

#IFDTと#CTの値から、テストポイント挿入によって、c432、c1355のテストパターン数が逆に増大していることがわかった。また、表4において、Cirは回路名、#T\_PATはテストパターン数、#ATTPはテストポイント挿入後の故障検出数、AFCはテストポイント挿入後の故障検出率、#BTTPはテストポイント挿入前の故障検出率、#BTTPはテストポイント挿入前の故障検出数、BFCはテストポイント挿入前の故障検出率を表す。回路の故障検出率は式(10)と式(11)により求められる.

$$AFC = \frac{\#ADTP}{\#ATTP} \times 100 \qquad (10)$$

$$BFC = \frac{\#BDTP}{\#BTTP} \times 100 \qquad (11)$$

表4 *ISCAS' 85*を用いた故障シミュレーションによる故障検出率の結果

| Cir   | #T_PAT | #ATTP | #ADTP | AFC(%) | #BTTP | #BDTP | BFC(%) |

|-------|--------|-------|-------|--------|-------|-------|--------|

| c432  | 100    | 532   | 454   | 85.34  | 524   | 462   | 88.17  |

| c880  | 100    | 958   | 869   | 90.71  | 942   | 856   | 90.87  |

| c1355 | 100    | 1600  | 1407  | 87.94  | 1574  | 1416  | 89.96  |

| c1908 | 100    | 1917  | 1520  | 79.29  | 1879  | 1427  | 75.94  |

| c2670 | 100    | 2801  | 2534  | 90.47  | 2747  | 2169  | 78.96  |

| c3540 | 100    | 3498  | 2948  | 84.28  | 3428  | 2764  | 80.63  |

| c5315 | 100    | 5456  | 5226  | 95.78  | 5350  | 5001  | 93.48  |

| c6288 | 100    | 7868  | 7830  | 99.52  | 7744  | 7706  | 99.51  |

| c7552 | 100    | 7696  | 7031  | 91.36  | 7550  | 6485  | 85.89  |

AFCとBFCの値から, c432, c880, c1908, c1355 はテストポイント挿入によって, 逆に故障検出率が落ちている.

c432, c880, c1908における回路の実験結果を 比べると, 表4での故障検出率が小さくなると, ランダムパターンによる故障検出が困難にな り, 表2では大量のランダムパターンが必要と する. 逆に, 故障検出が大きくなると, 少ない ランダムパターンで故障を容易に検出できる ことがわかる.

#### 6 まとめ

本稿では、テストパターン数を削減するために、COPベースに基づくテストポイント挿入のためのコスト関数を定義した.

今後の課題として、ランダムパターンテスタ ビリティに基づくテストポイント挿入法によ る実装を行う.

#### 「参考文献」

- 1) C. Schotten and H. Meyr. Test Point insertion for an area efficient bist. *Proc.* Of the *IEEE* Int. Test Conf., page 515-523, 1995.

- 2) R. Lisanke, F. Brglez, A. J. Degeus and D. Gregory. Testability-driven random test-pattern generation. *IEEE* Transactions on Computer-Aided Design, CAD-6:1082, 1987.

- 3) B. H. Seiss, P. M. Trouorst and M. H Schulz. Test point insertion for scan-based bist. *Proc.* Of 2<sup>nd</sup> European Test Conf., pages 253-262, 1991.

- 4) 吉村正義, 細川利典, 太田光保, "テストパターン数削減指向テストポイント挿入方法,"信学論, vol. J86-D-I, no. 12, PP. 884-896, 2003.

- 5) 藤原秀雄, "ディジタルシステムの設計とテスト,"工学図書,2004.

- 6) 斉藤善洋," 故障検出確率及び改善故障 検出確率に基づくテストパターン数削減のた めのテストポイント挿入法", 2005.